# Aspects of Computer Architecture

T V Atkinson, Ph D

Senior Academic Specialist

Department of Chemistry

Michigan State University

East Lansing, MI 48824

## Table of Contents

|                                                                      |    |

|----------------------------------------------------------------------|----|

| List of Tables .....                                                 | 3  |

| List of Figures .....                                                | 3  |

| 1. Introduction.....                                                 | 6  |

| 1.1. Why should Chemists care about this material? .....             | 6  |

| 1.2. How can we characterize the people who use computers? .....     | 6  |

| 1.2.1. By the Type of Use .....                                      | 6  |

| 1.2.2. By frequency of use of a particular program or facility ..... | 6  |

| 1.2.3. By level of expertise for a given program or facility.....    | 6  |

| 2. Number Systems .....                                              | 7  |

| 2.1. Range of Numbers .....                                          | 8  |

| 2.2. Converting Between Different Moduli .....                       | 8  |

| 2.2.1. Binary to/from Hexadecimal.....                               | 8  |

| 2.2.2. Binary to/from Octal .....                                    | 10 |

| 2.3. Signed Integers .....                                           | 12 |

| 2.3.1. Sign/Magnitude.....                                           | 12 |

| 2.3.2. One's Complement .....                                        | 13 |

| 2.3.3. Two's Complement .....                                        | 14 |

| 2.4. Floating Point Numbers .....                                    | 16 |

| 2.5. Useful Tables of Numbers .....                                  | 19 |

| 2.5.1. Powers of Two .....                                           | 19 |

| 3. Character Codes .....                                             | 25 |

| 3.1. Six Bit Character Codes.....                                    | 25 |

| 3.2. ASCII Character Codes .....                                     | 26 |

| 3.3. ANSI Character Codes.....                                       | 28 |

| 3.4. Unicode Character Codes .....                                   | 29 |

| 4. Logic .....                                                       | 31 |

| 4.1. Single Bit Logic Truth Tables .....                             | 31 |

| 4.2. Multibit Logic Examples .....                                   | 31 |

| 5. Gates and Latches .....                                           | 33 |

| 6. Simple Computer .....                                             | 35 |

| 6.1. Digital Buses.....                                              | 35 |

| 6.1.1. A Simple Example .....                                        | 36 |

| 6.1.2. A 4-Bit Bus .....                                             | 39 |

| 6.1.3. An 8-Bit Bus System .....                                     | 41 |

| 6.1.4. A Simple Input/Output System.....                             | 43 |

# Aspects of Computer Architecture

## List of Tables

|                                                                 |     |

|-----------------------------------------------------------------|-----|

| 6.1.5. A More Complete I/O Bus Architecture.....                | 44  |

| 6.1.5.1. Reads.....                                             | 48  |

| 6.1.5.2. Writes.....                                            | 49  |

| 6.2. Post Office (Programmers) Model of Computing .....         | 50  |

| 6.3. Uses of collections of n binary bits.....                  | 51  |

| 6.4. Instruction Sets .....                                     | 51  |

| 6.5. Addressing .....                                           | 53  |

| 6.6. Operation .....                                            | 53  |

| 6.7. An Example Computer .....                                  | 54  |

| 6.7.1. Registers.....                                           | 54  |

| 6.7.2. Instruction format .....                                 | 55  |

| 6.7.3. Instruction Set .....                                    | 56  |

| 6.7.4. An Example Program.....                                  | 57  |

| 6.7.5. Example Program 2.....                                   | 61  |

| 6.7.6. An Example Application of Hardware and Software .....    | 64  |

| 6.7.7. Sample Program.....                                      | 67  |

| 7. Computer Architecture Taxonomy .....                         | 72  |

| 7.1. Special Buses .....                                        | 72  |

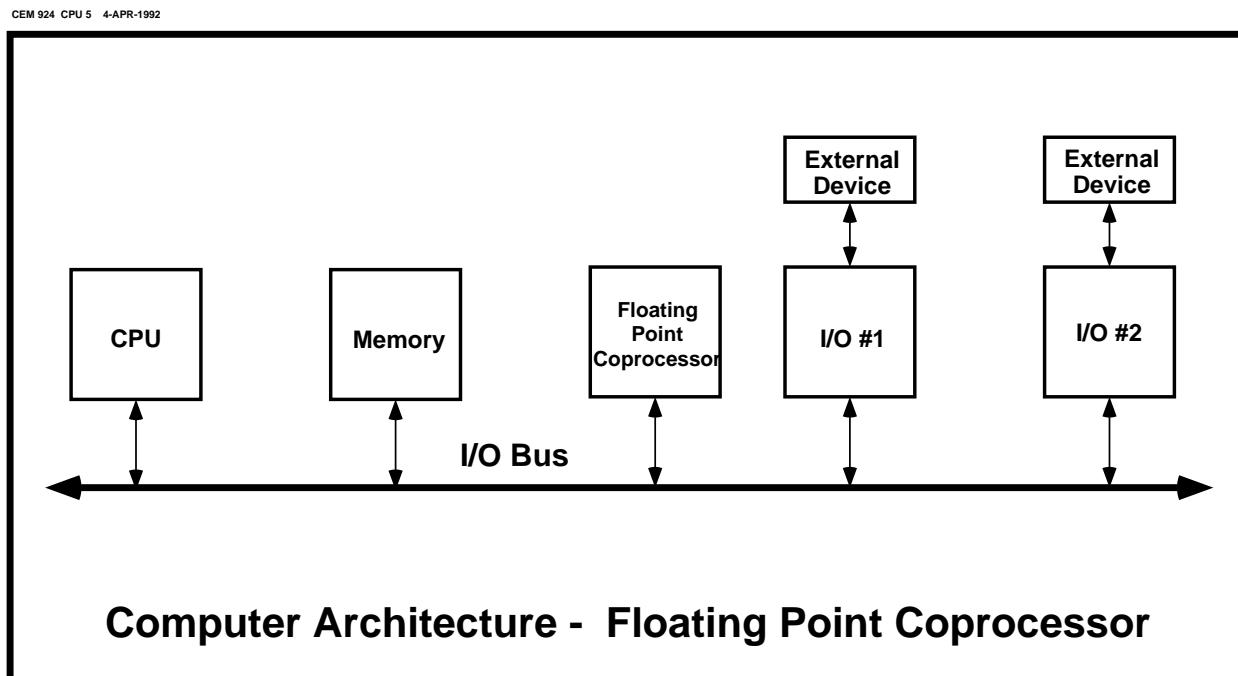

| 7.2. Coprocessors .....                                         | 73  |

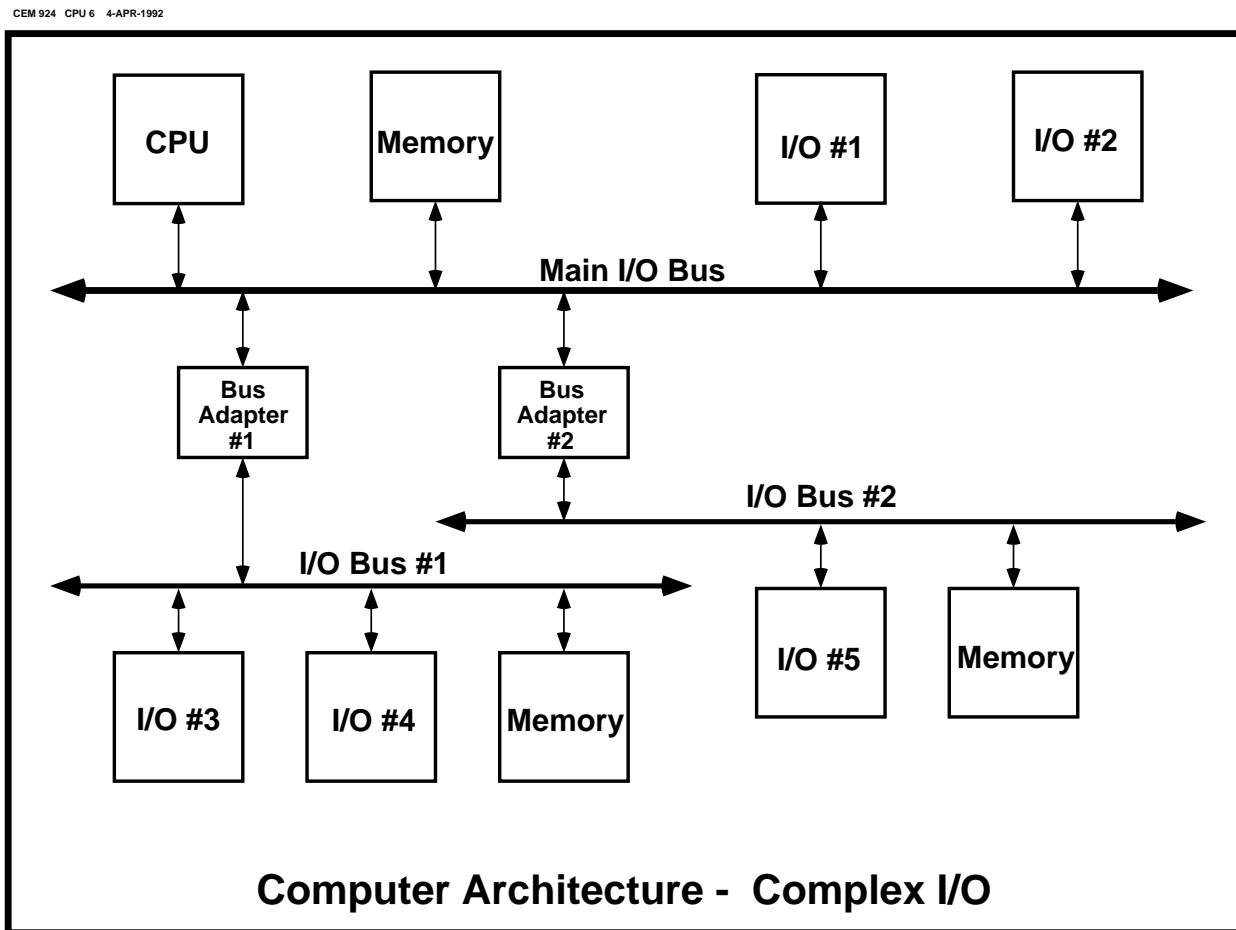

| 7.3. Multiple I/O buses .....                                   | 74  |

| 7.3.1. Problems .....                                           | 76  |

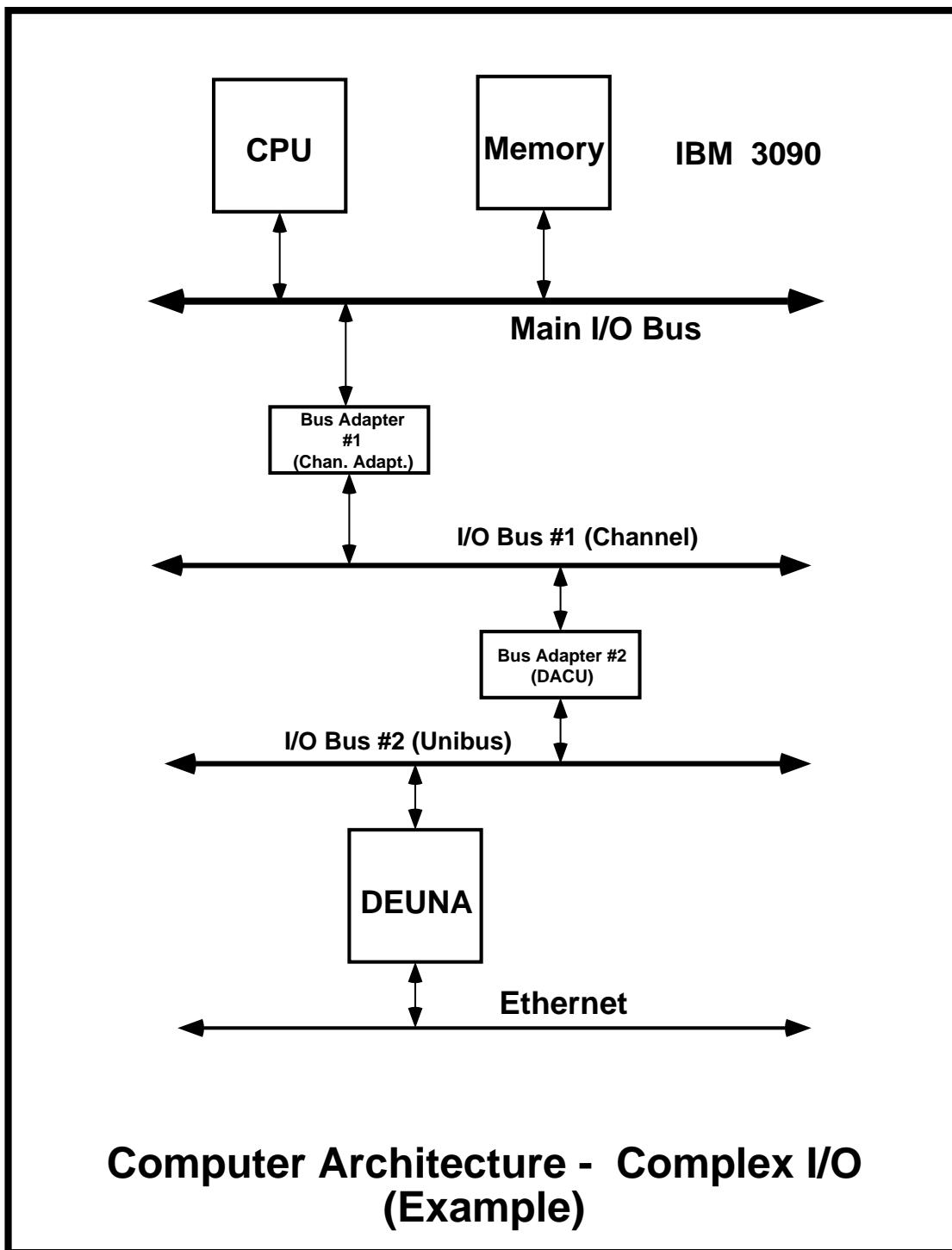

| 7.3.2. Examples .....                                           | 76  |

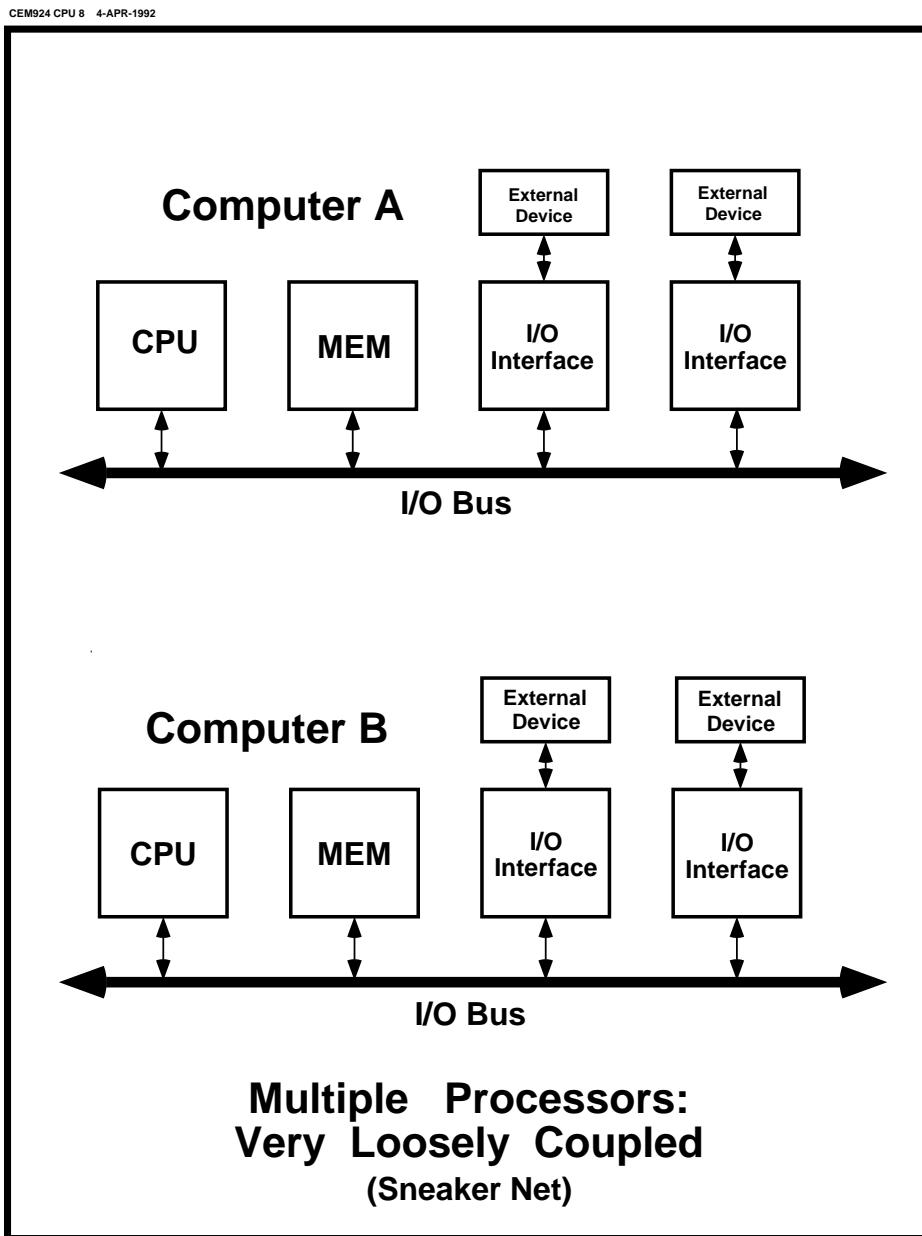

| 8. Multiple Processors.....                                     | 77  |

| 9. Disk Drives .....                                            | 80  |

| 9.1. General Architecture.....                                  | 80  |

| 9.2. Disk Format .....                                          | 83  |

| 9.3. Mapping Sectors into Logical Blocks.....                   | 85  |

| 9.4. Figures of Merit for a Disk .....                          | 86  |

| 9.5. Combinations of Disks.....                                 | 87  |

| 9.5.1. Combinations of Simple Disks .....                       | 88  |

| 10. Memory Utilization.....                                     | 93  |

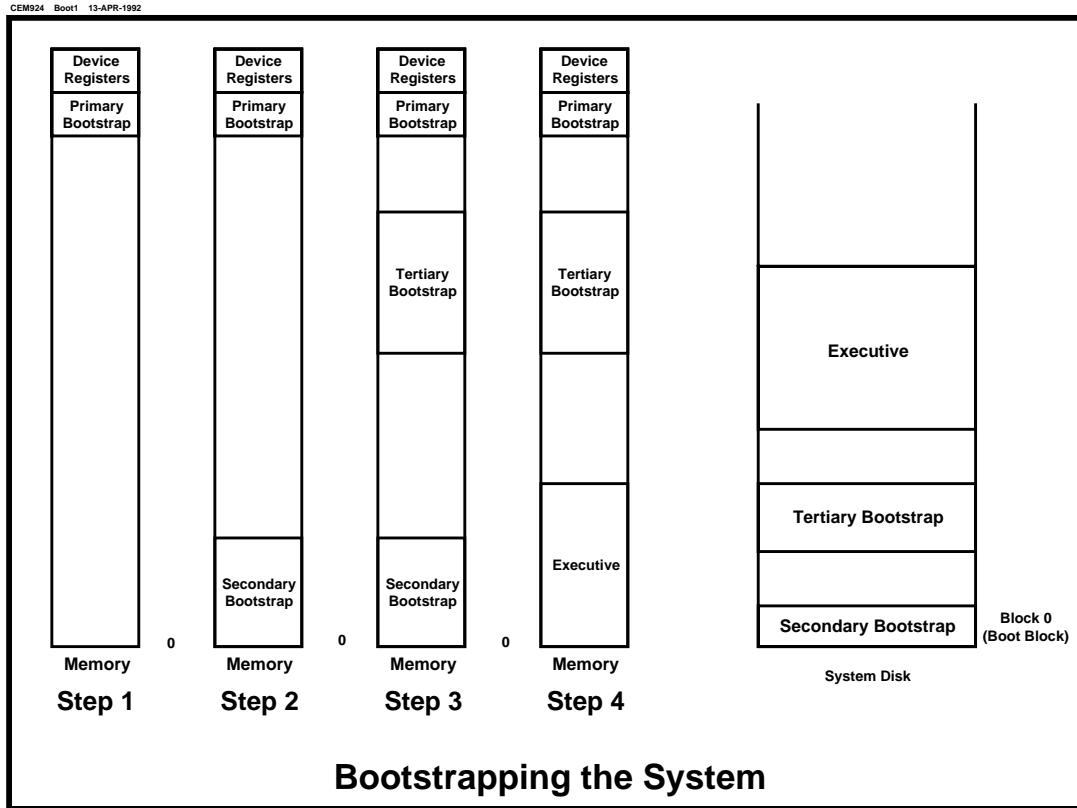

| 11. Boot Straps.....                                            | 94  |

| 11.1. Simple .....                                              | 94  |

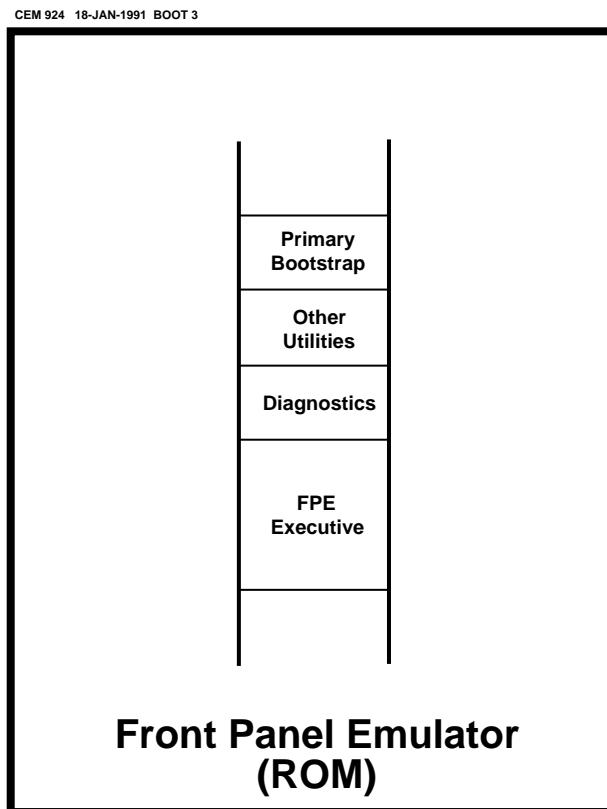

| 11.2. Typical of Modern Machines with a Volatile Executive..... | 95  |

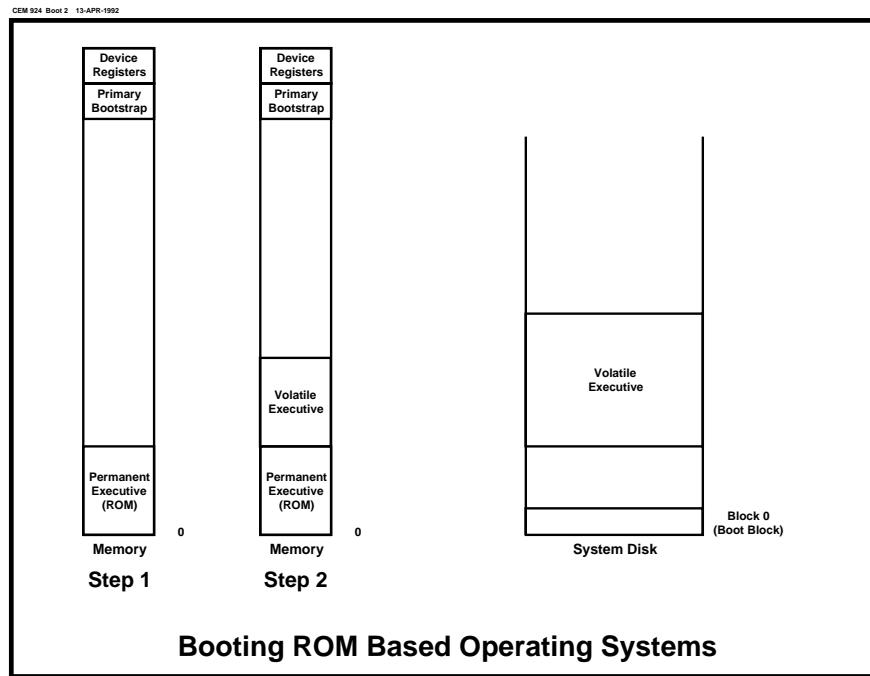

| 11.3. Machines with a ROM based Operating System .....          | 97  |

| 12. Memory Systems .....                                        | 98  |

| 13. Increasing Performance .....                                | 100 |

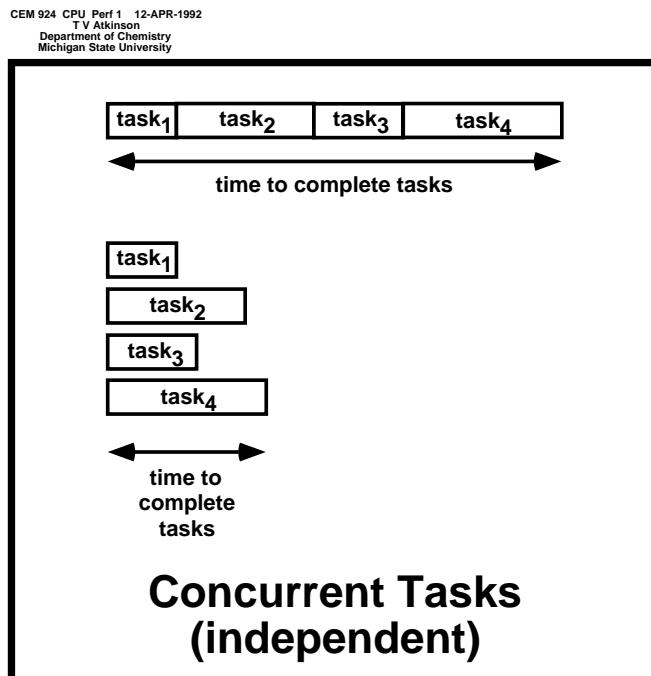

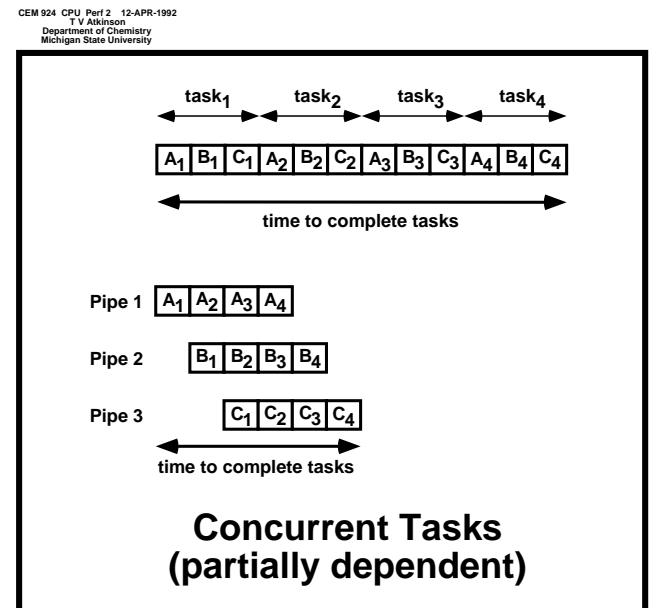

| 13.1. Concurrent Tasks .....                                    | 102 |

| 13.1.1. Tasks are completely independent.....                   | 102 |

| 13.1.2. Pipelines (Tasks are somewhat independent) .....        | 103 |

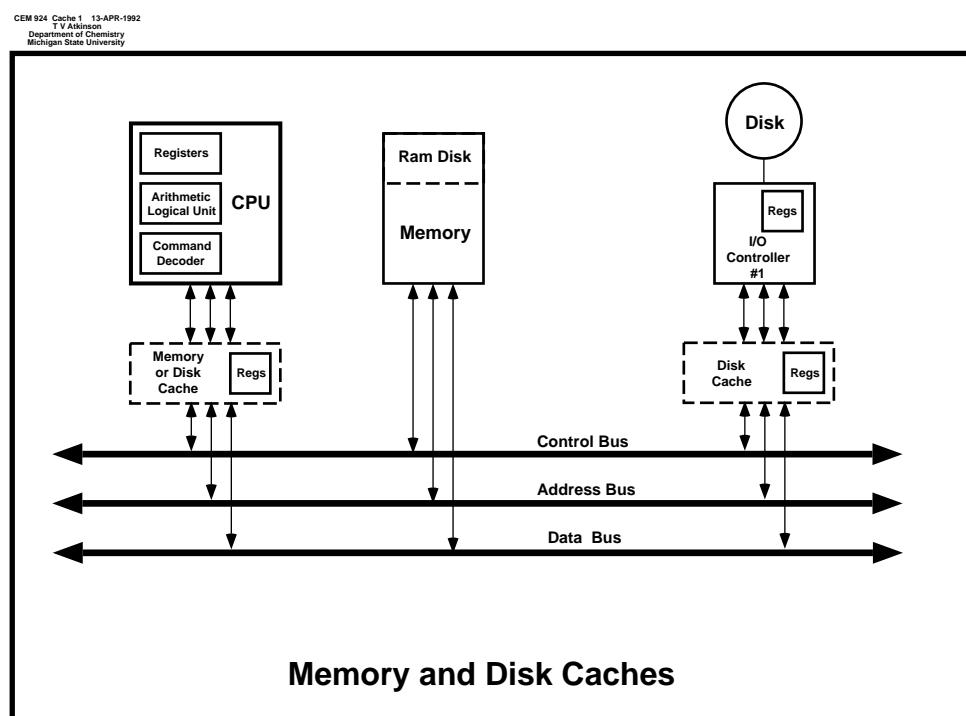

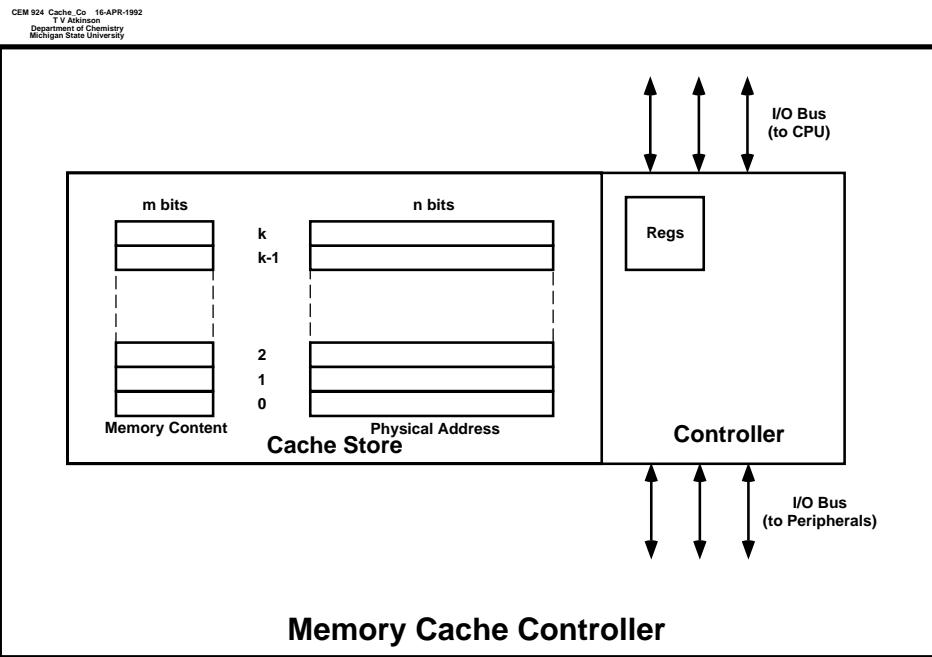

| 13.1.3. Cache.....                                              | 103 |

| 13.1.4. Direct Memory Access (DMA) .....                        | 106 |

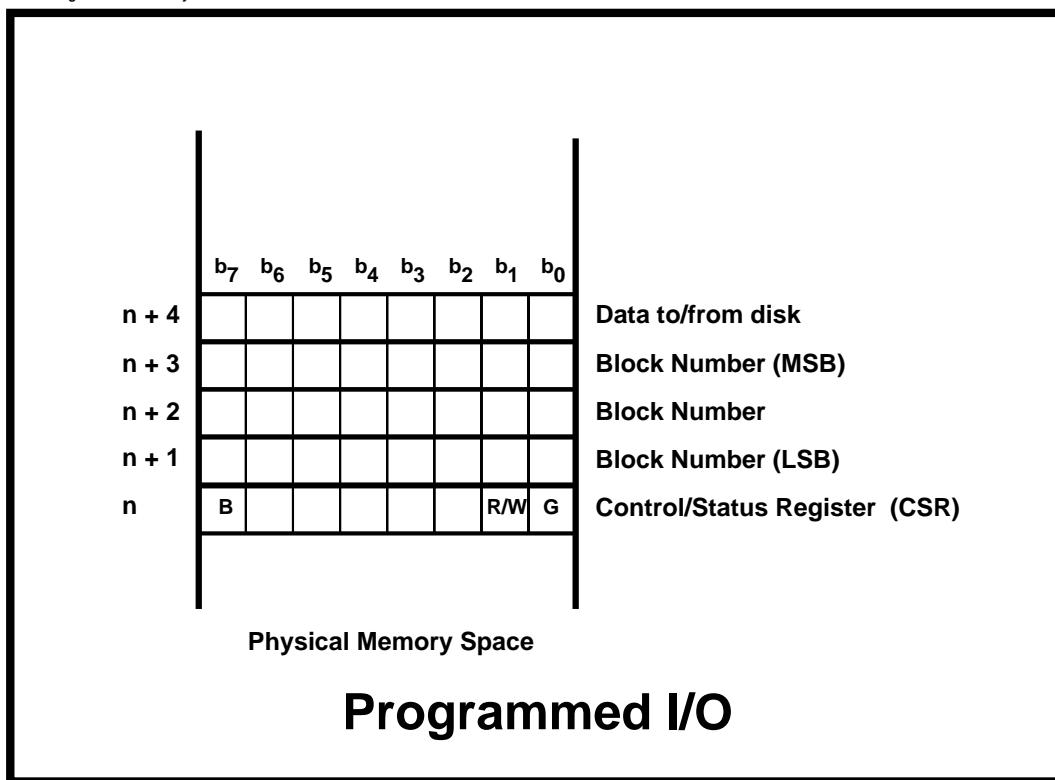

| 13.1.4.1. Programmed I/O (Example: reading a block of data) ..  | 106 |

| 13.1.4.2. Asynchronous I/O (Interrupt Structures) .....         | 107 |

| 13.1.4.2.1. Interrupt Structure 1 .....                         | 107 |

# Aspects of Computer Architecture

## List of Tables

|                                                          |     |

|----------------------------------------------------------|-----|

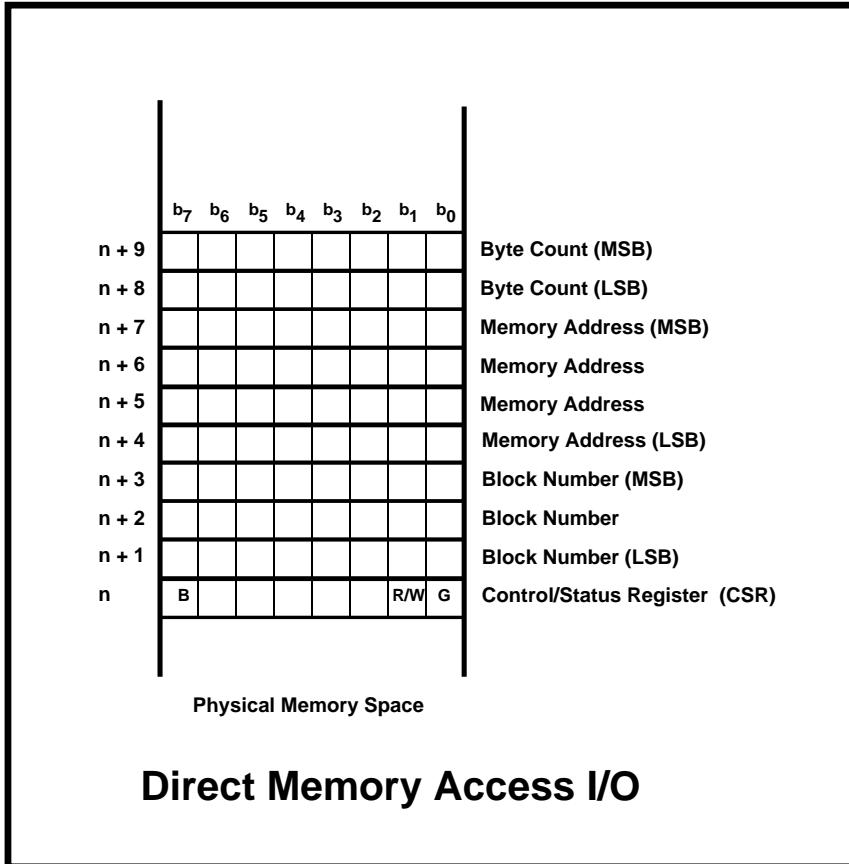

| 13.1.4.3. DMA I/O (Example: Write a block to disk) ..... | 109 |

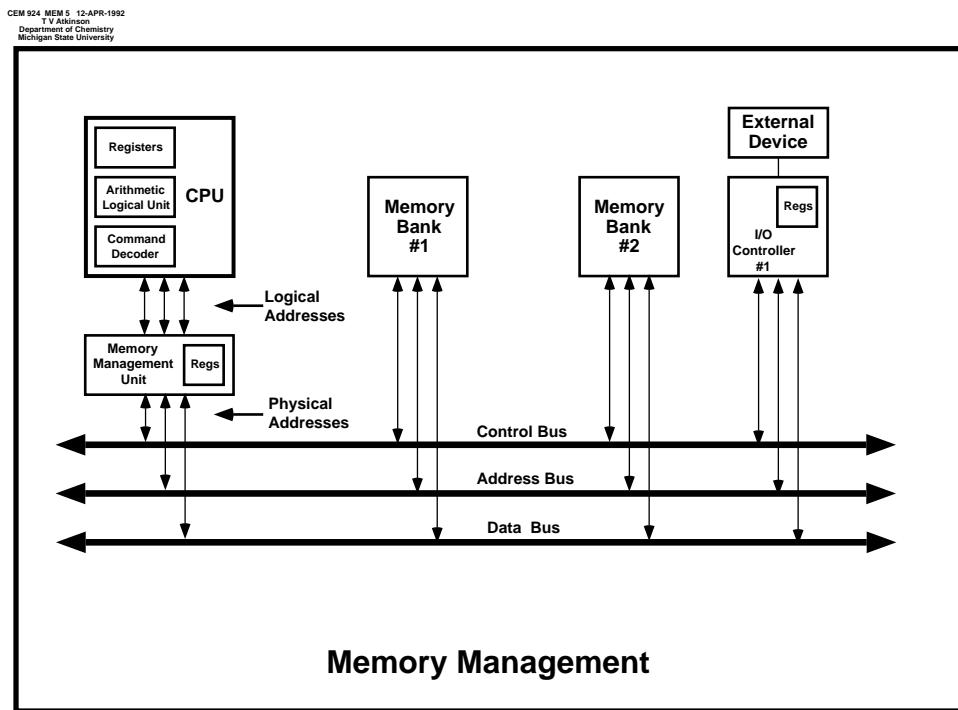

| 14. Memory Management.....                               | 110 |

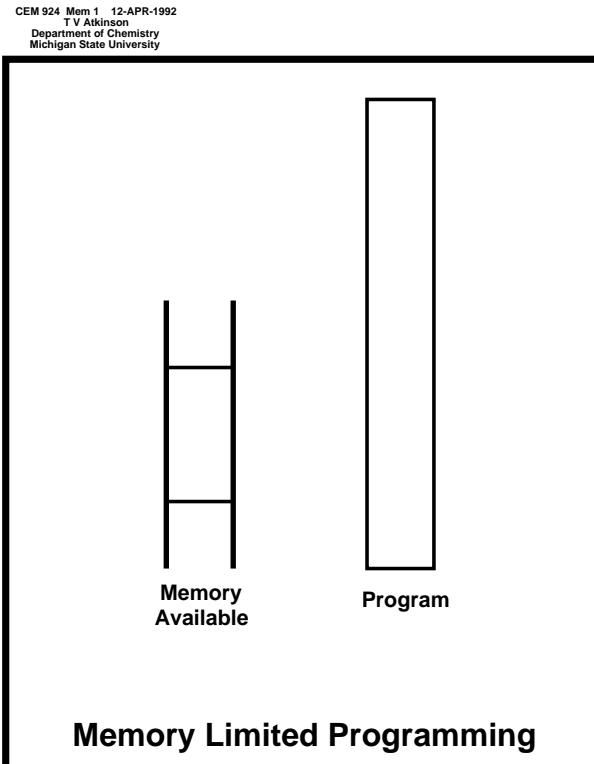

| 14.1. Introduction.....                                  | 110 |

| 14.2. Motivations for Memory Management.....             | 112 |

| 14.3. Software solutions.....                            | 112 |

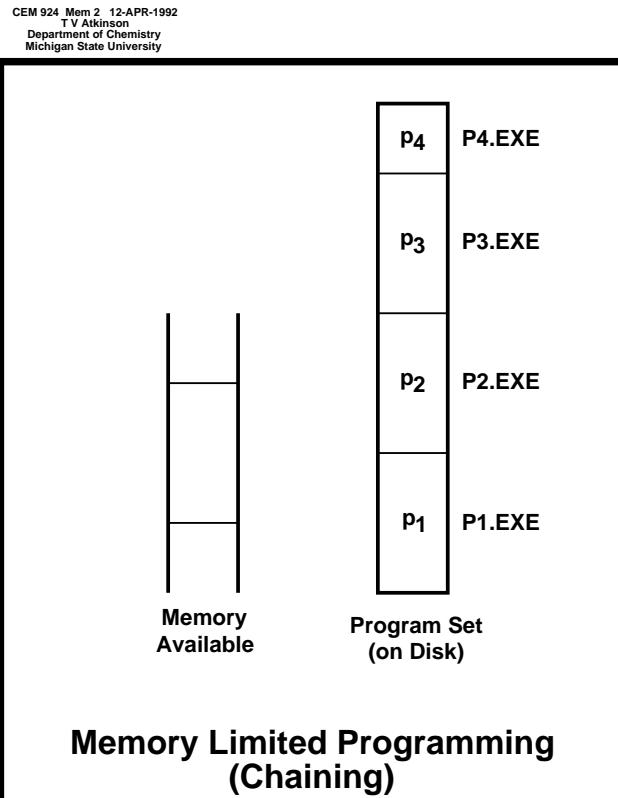

| 14.3.1. Chaining.....                                    | 112 |

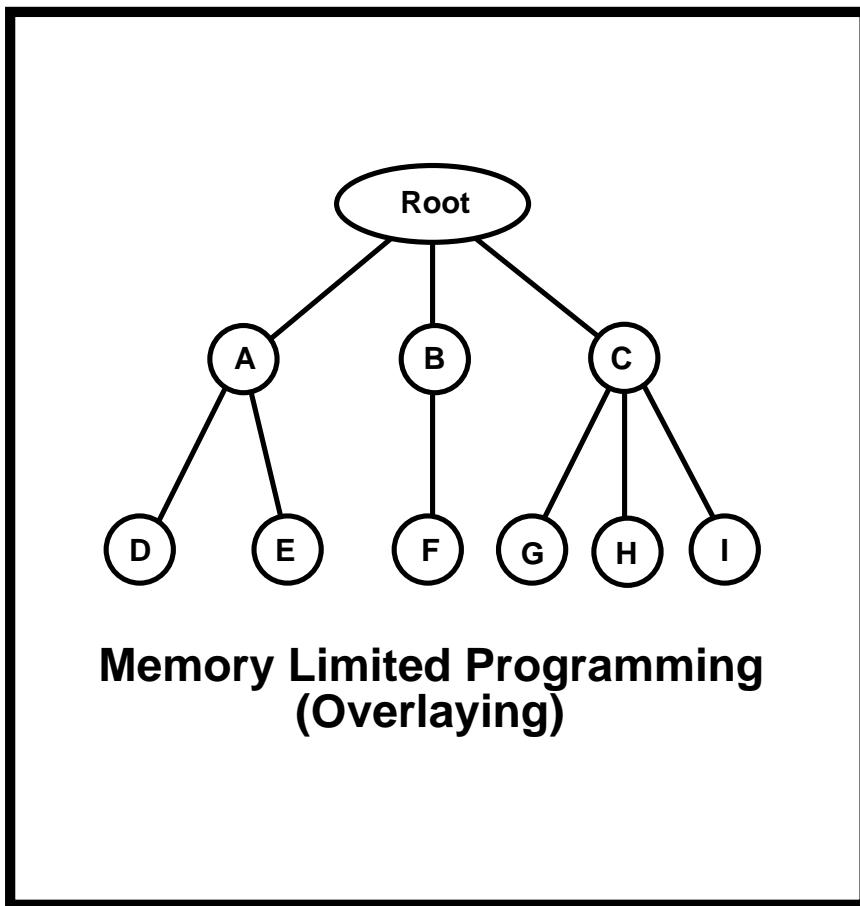

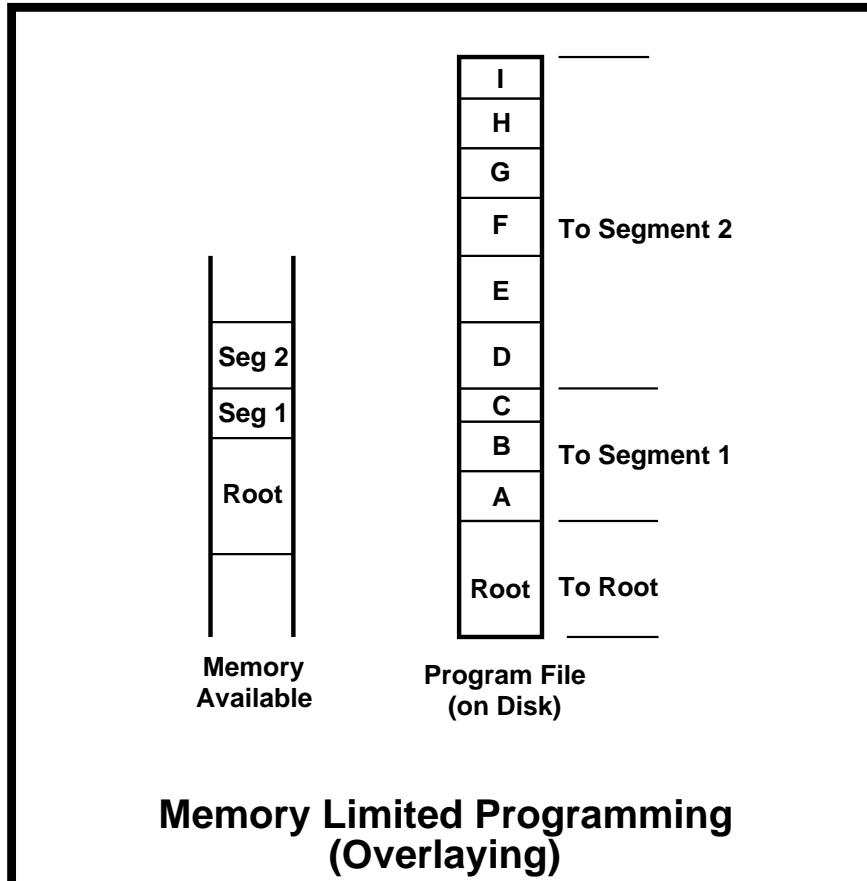

| 14.3.2. Overlaying .....                                 | 113 |

| 14.4. Hardware/Software Solutions .....                  | 115 |

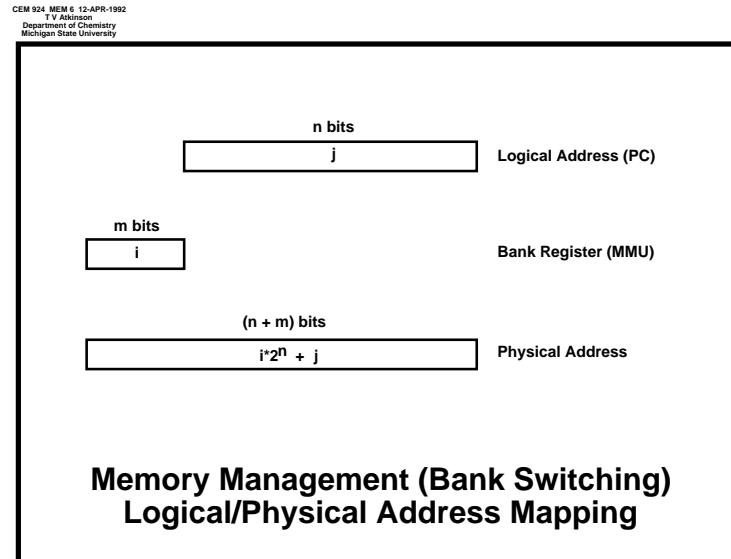

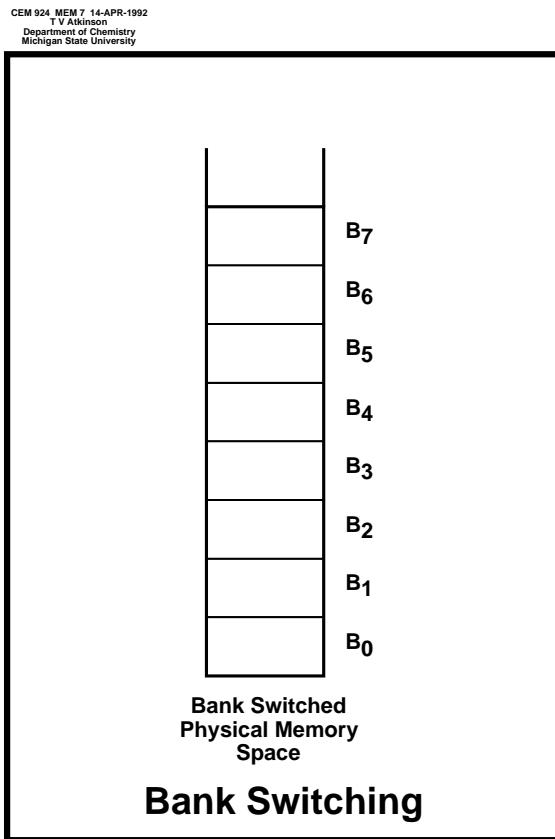

| 14.4.1. Bank Switching.....                              | 116 |

| 14.4.2. Bank Switching (Partial).....                    | 118 |

| 14.4.3. Segmentation.....                                | 121 |

| 14.4.4. Paging .....                                     | 123 |

| 14.4.5. Virtual Memory .....                             | 128 |

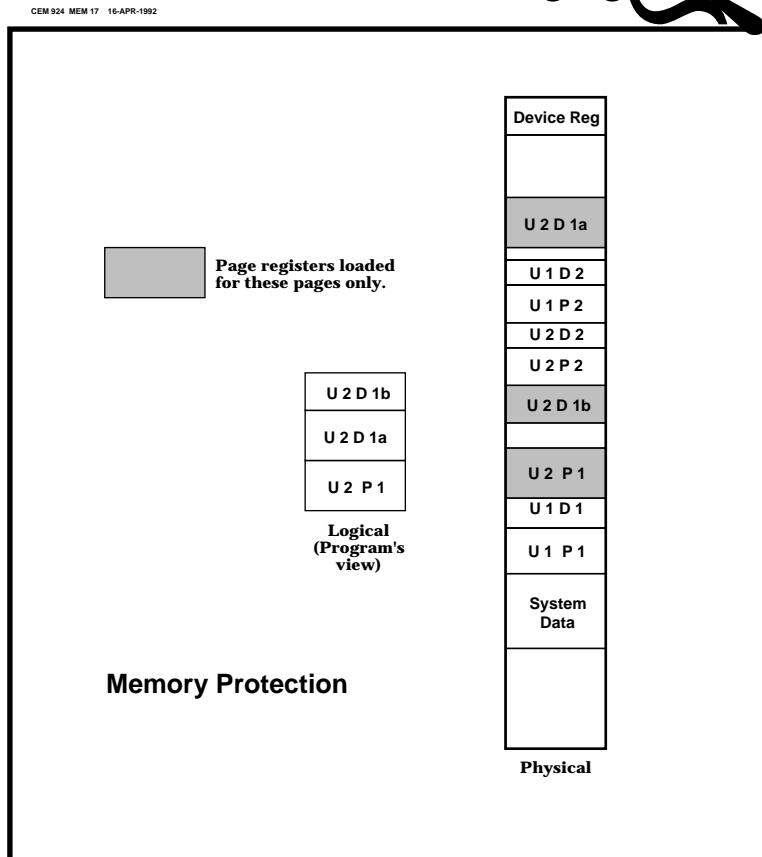

| 14.4.6. Memory Protection .....                          | 133 |

| 15. Value of a Particular Computing Environment .....    | 133 |

| 16. Measurement of Performance .....                     | 134 |

| 16.1. Benchmarks.....                                    | 134 |

| 17. CISC vs RISC .....                                   | 134 |

| 17.1. Main Attributes of RISC .....                      | 134 |

## List of Tables

|                                                                   |     |

|-------------------------------------------------------------------|-----|

| Table 1 Number Formats .....                                      | 17  |

| Table 2 Symbol Definitions .....                                  | 18  |

| Table 3 Powers of 2 .....                                         | 19  |

| Table 4 Counting in Different Moduli .....                        | 20  |

| Table 5 0 to 65536 in Multiple Moduli.....                        | 21  |

| Table 6 Six Bit Character Codes.....                              | 25  |

| Table 7 ASCII Character Codes .....                               | 26  |

| Table 8 ASCII Control Characters.....                             | 27  |

| Table 9 ANSI Character Set .....                                  | 28  |

| Table 10 UNICODE Character Codes .....                            | 30  |

| Table 11 Logic Truth Tables .....                                 | 31  |

| Table 12 Logic Examples .....                                     | 31  |

| Table 15 Disks: Mapping Physical Sectors into Logical Blocks..... | 86  |

| Table 16 Disks: Example Drives .....                              | 87  |

| Table 17 Powers of 2 (Abbreviated).....                           | 98  |

| Table 18 Representative Examples of DRAM Chips .....              | 99  |

| Table 19 Representative Examples of SIMMS.....                    | 100 |

## List of Figures

|                                             |    |

|---------------------------------------------|----|

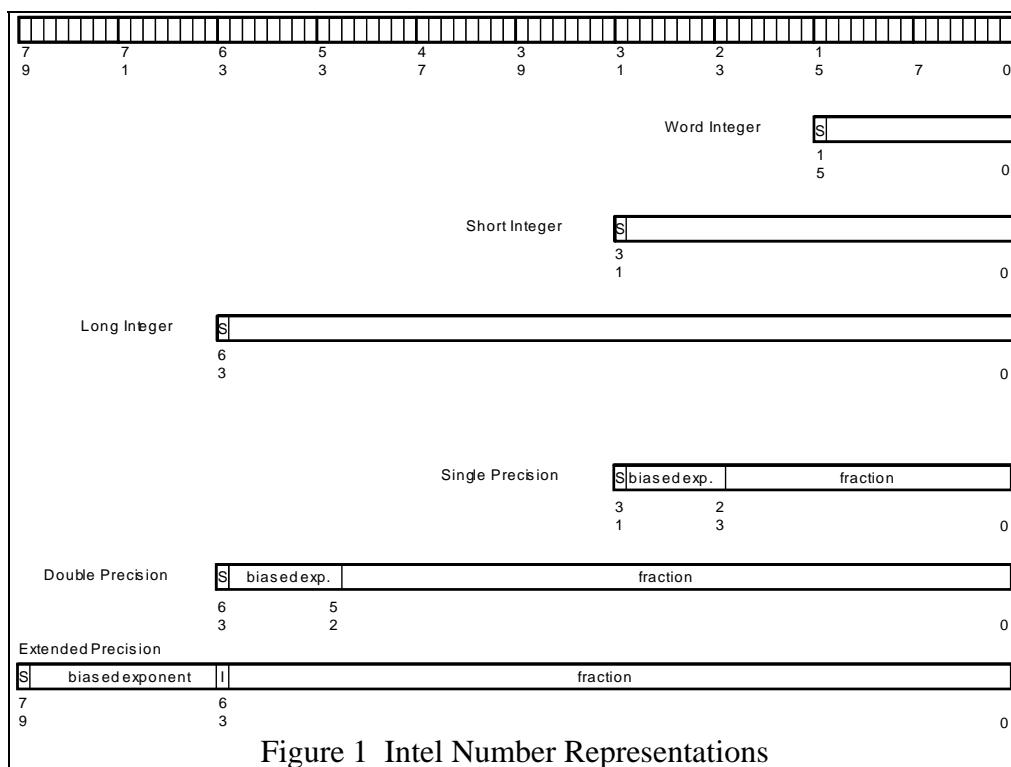

| Figure 1 Intel Number Representations ..... | 16 |

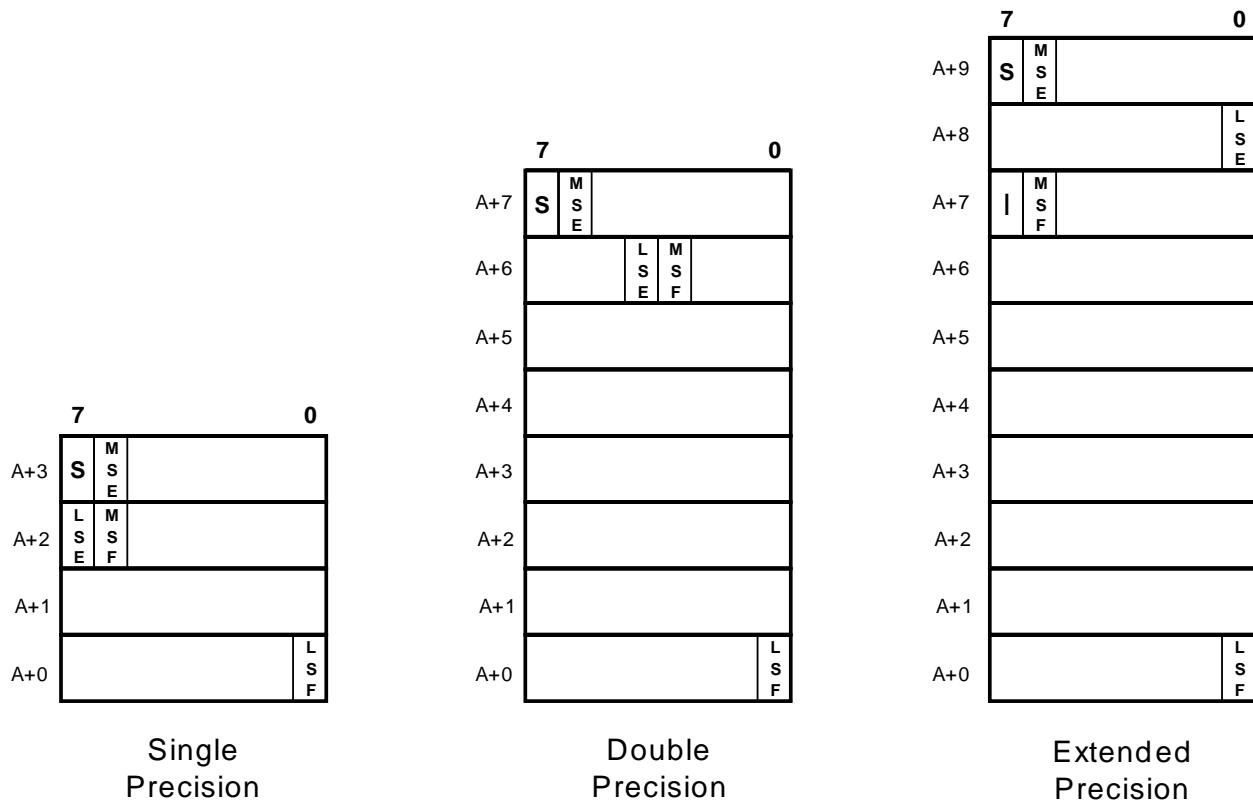

| Figure 2 Intel Floating Point Storage.....  | 17 |

| Figure 3 Intel Integer Storage .....        | 18 |

# Aspects of Computer Architecture

## List of Figures

|                                                                     |    |

|---------------------------------------------------------------------|----|

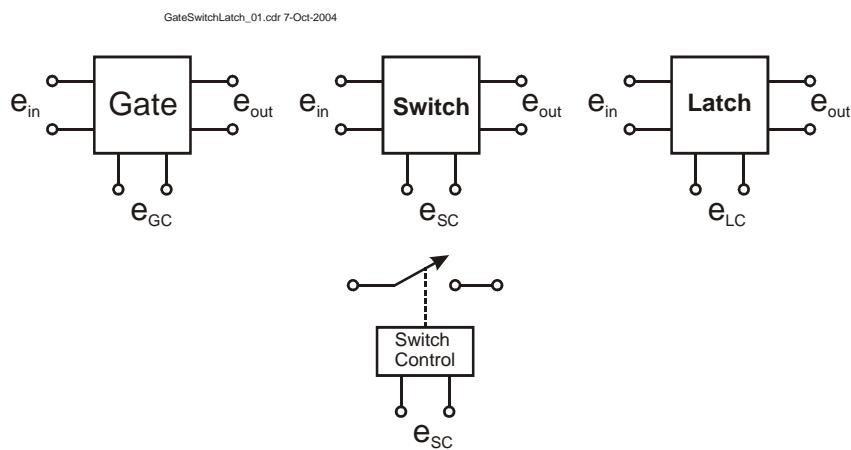

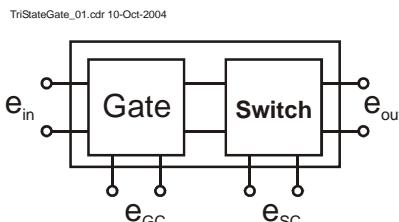

| Figure 4 Generic Gate, Switch, and Latch.....                       | 33 |

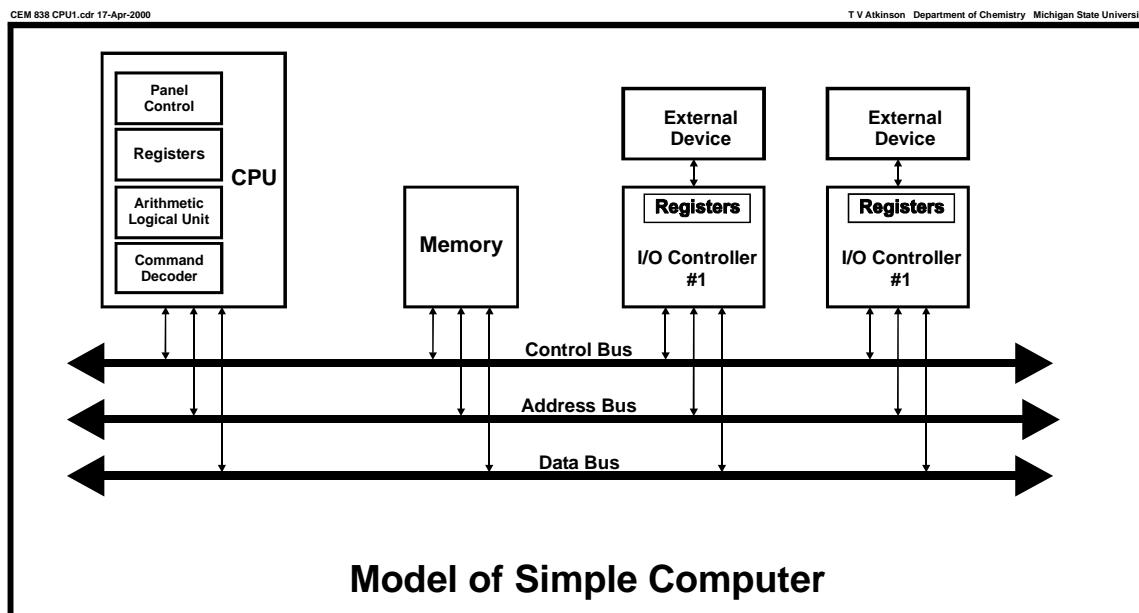

| Figure 6 Von Neumann Model of Computer.....                         | 35 |

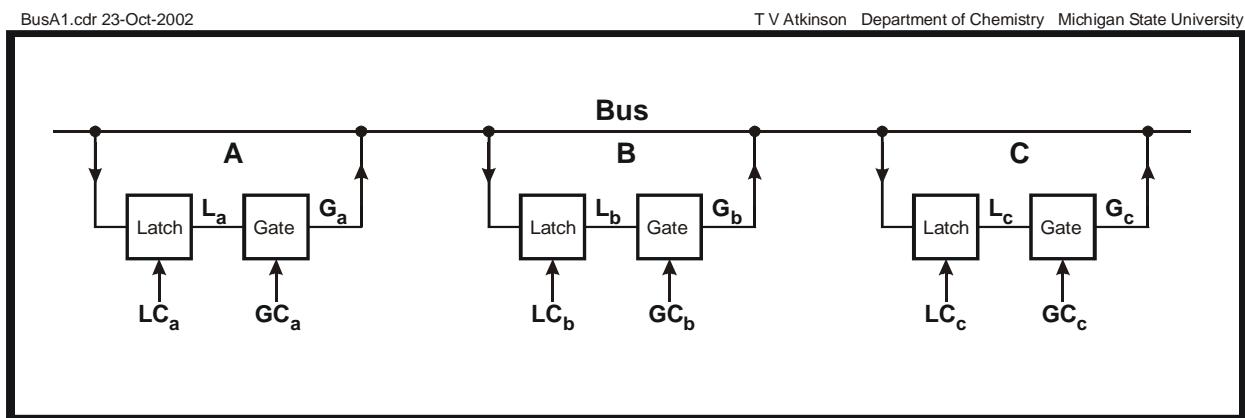

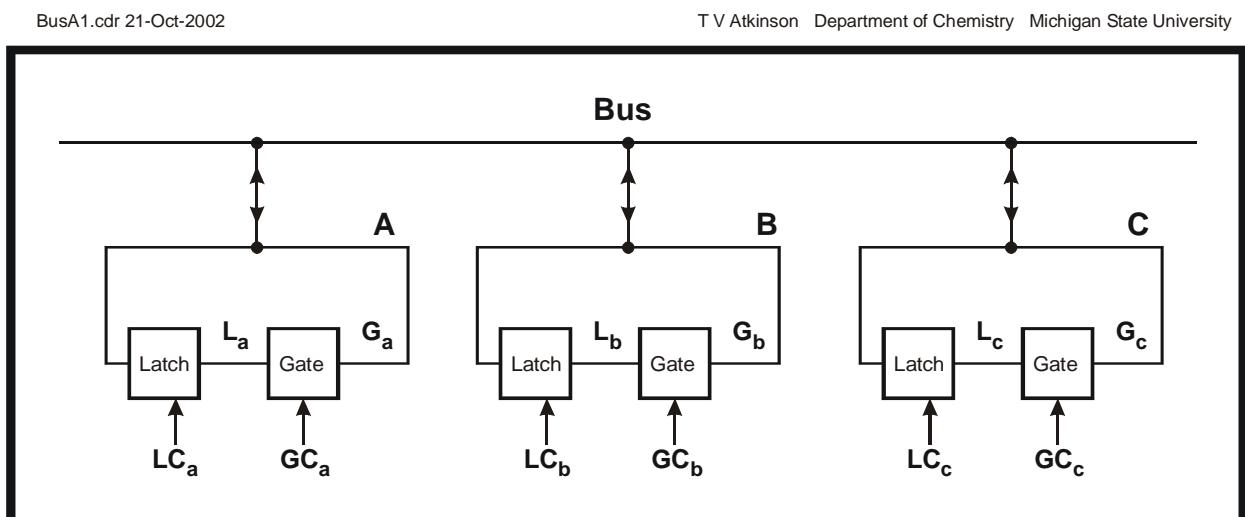

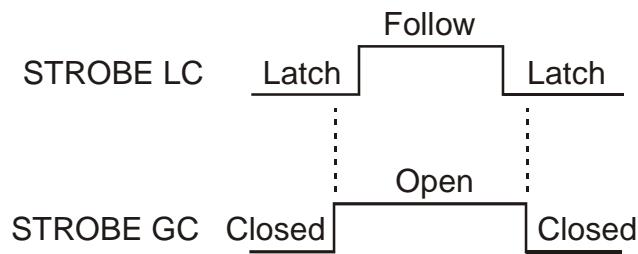

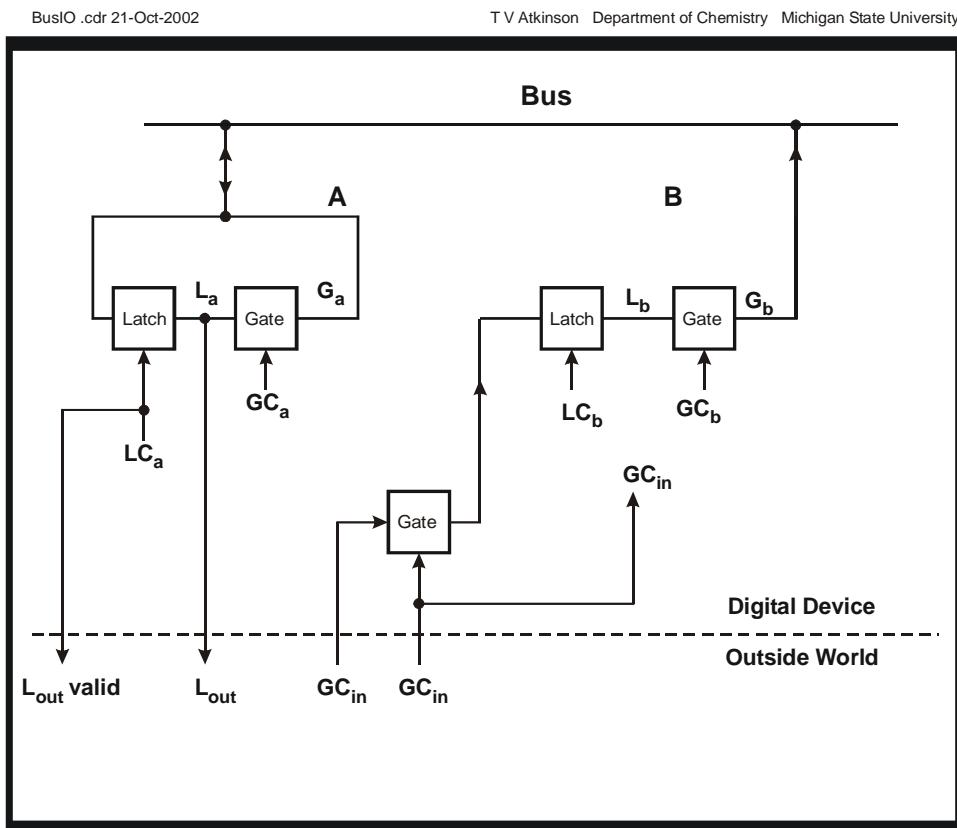

| Figure 7 Strobe.....                                                | 37 |

| Figure 8 A Digital Bus with Three Devices .....                     | 37 |

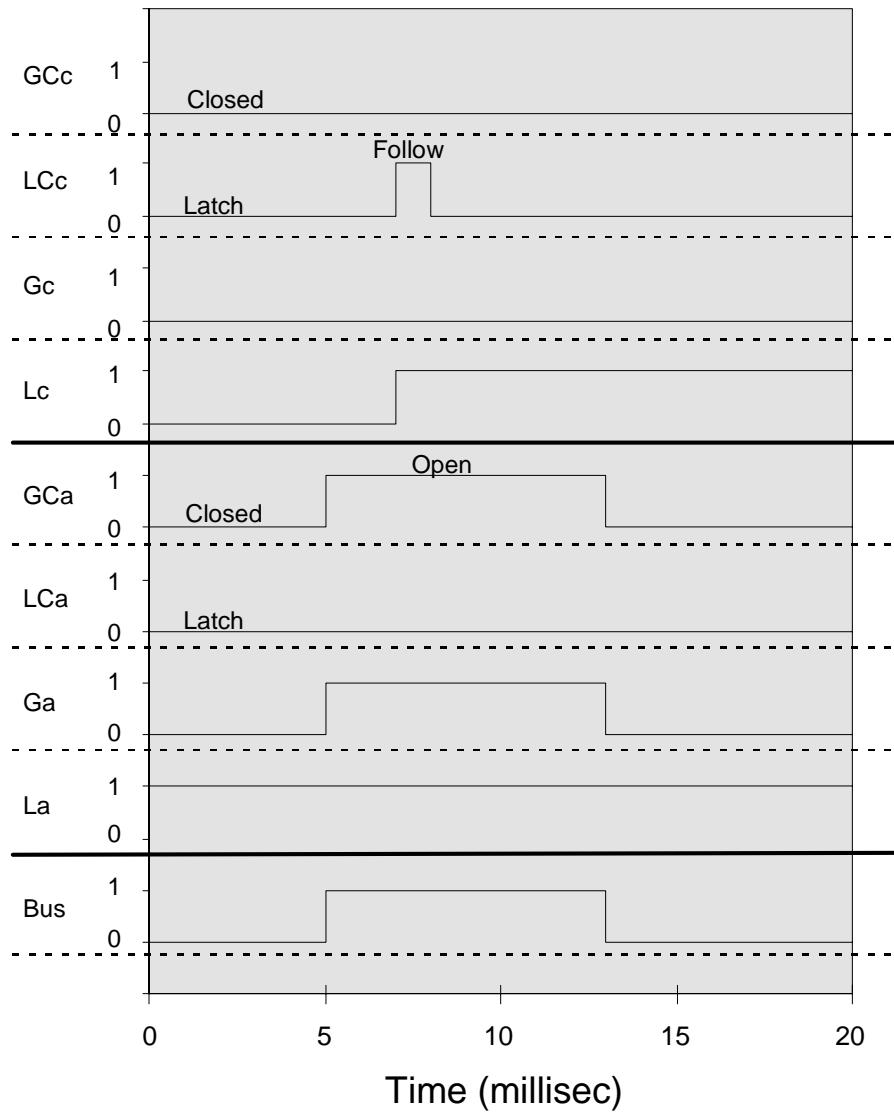

| Figure 9 A 1-Bit Bus with Three Devices (Equivalent Schematic)..... | 37 |

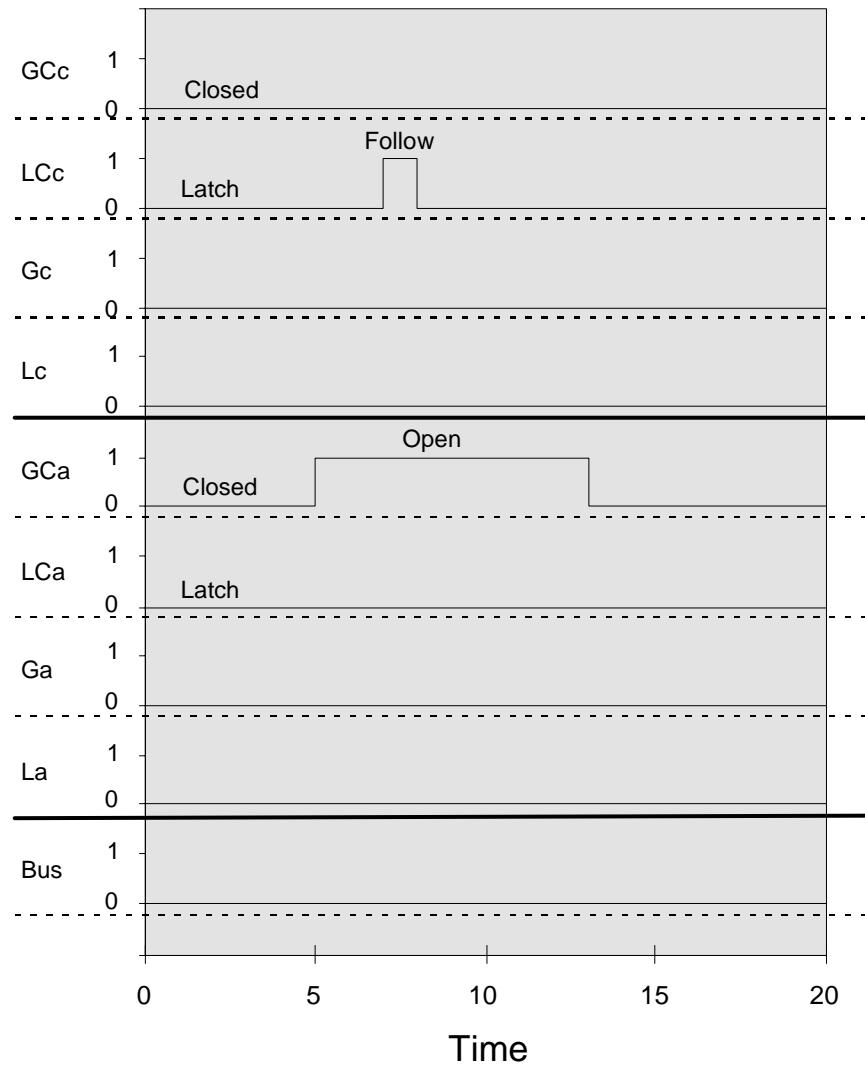

| Figure 10 Timing - Transfer Contents of A (1) to C .....            | 38 |

| Figure 11 Timing - Transfer Contents of A (0) to C .....            | 39 |

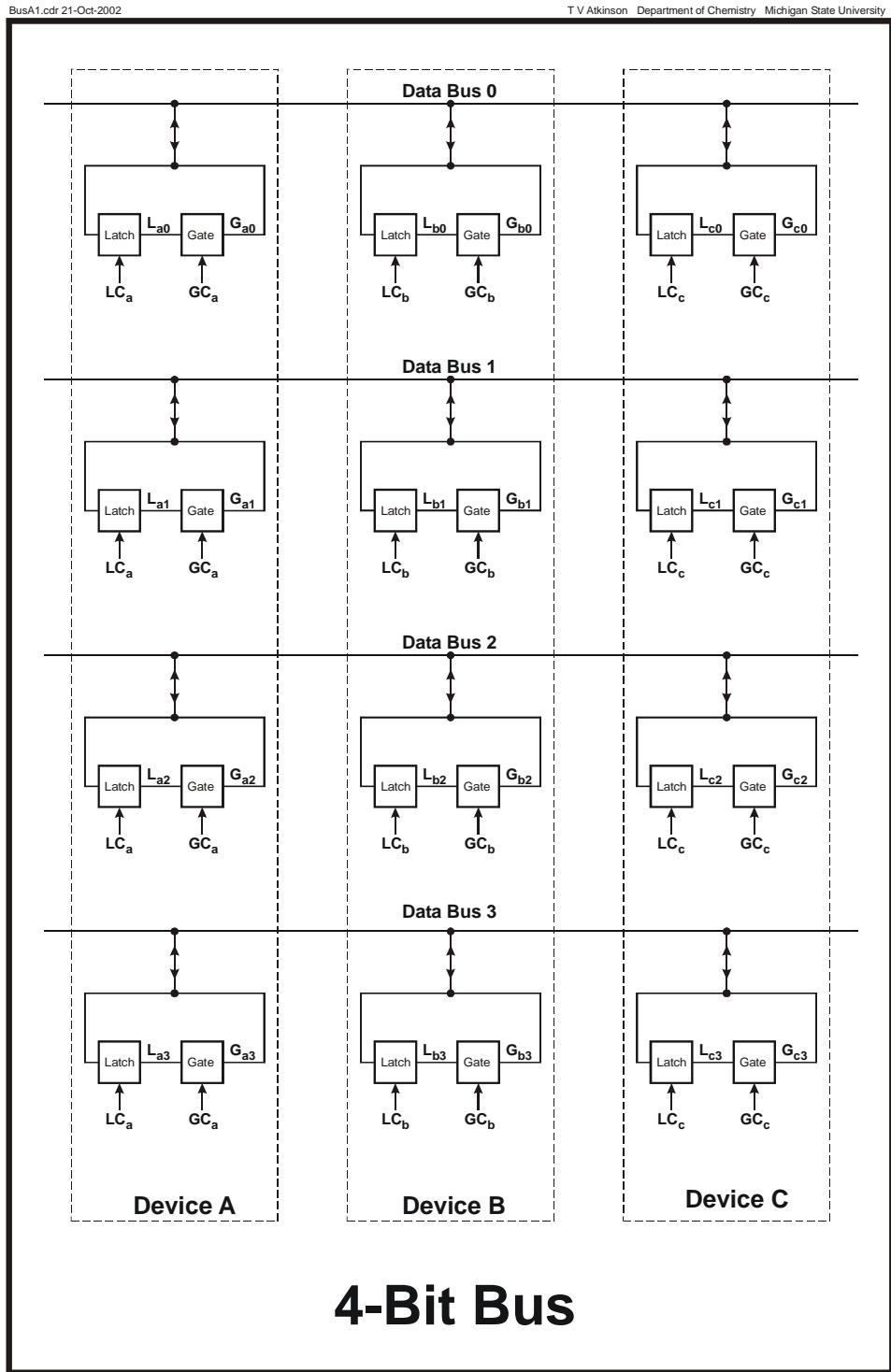

| Figure 12 4-Bit Bus.....                                            | 40 |

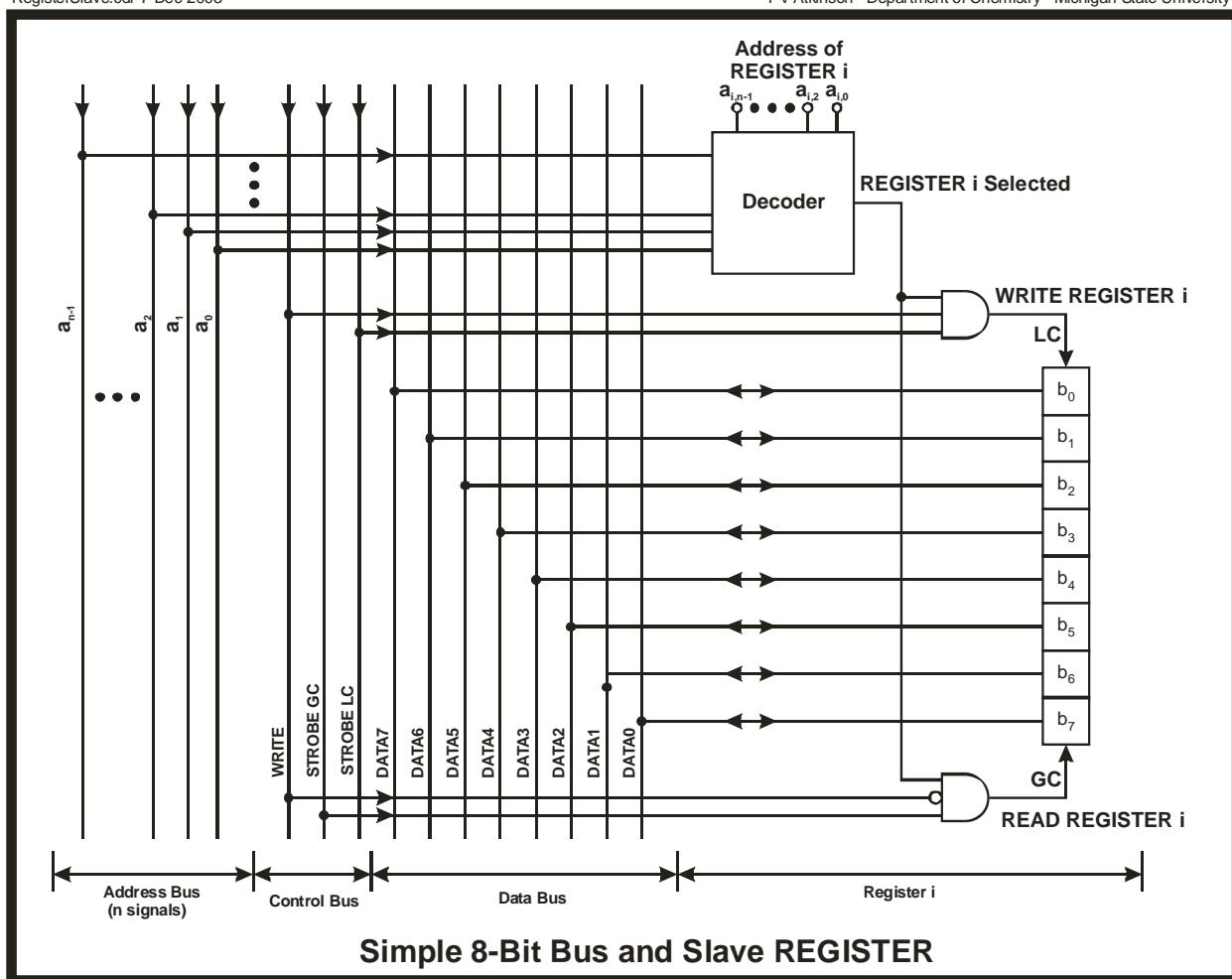

| Figure 13 Simple 8-Bit Bus and Slave Register .....                 | 41 |

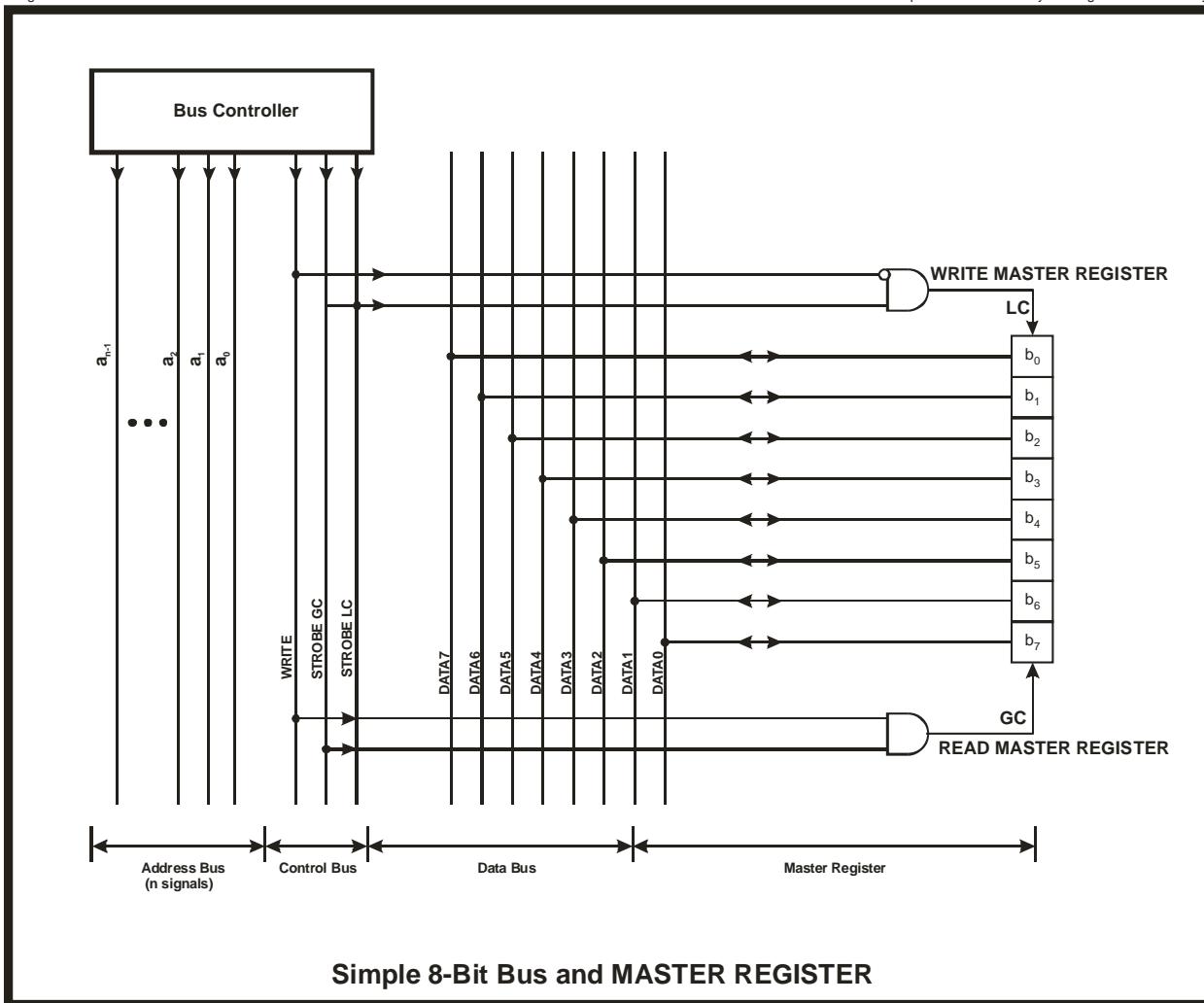

| Figure 14 - Simple 8-Bit Bus and Master Register.....               | 42 |

| Figure 15 Simple 8-Bit Bus and Master Register .....                | 43 |

| Figure 16 Simple 8-Bit Bus and Master Register .....                | 43 |

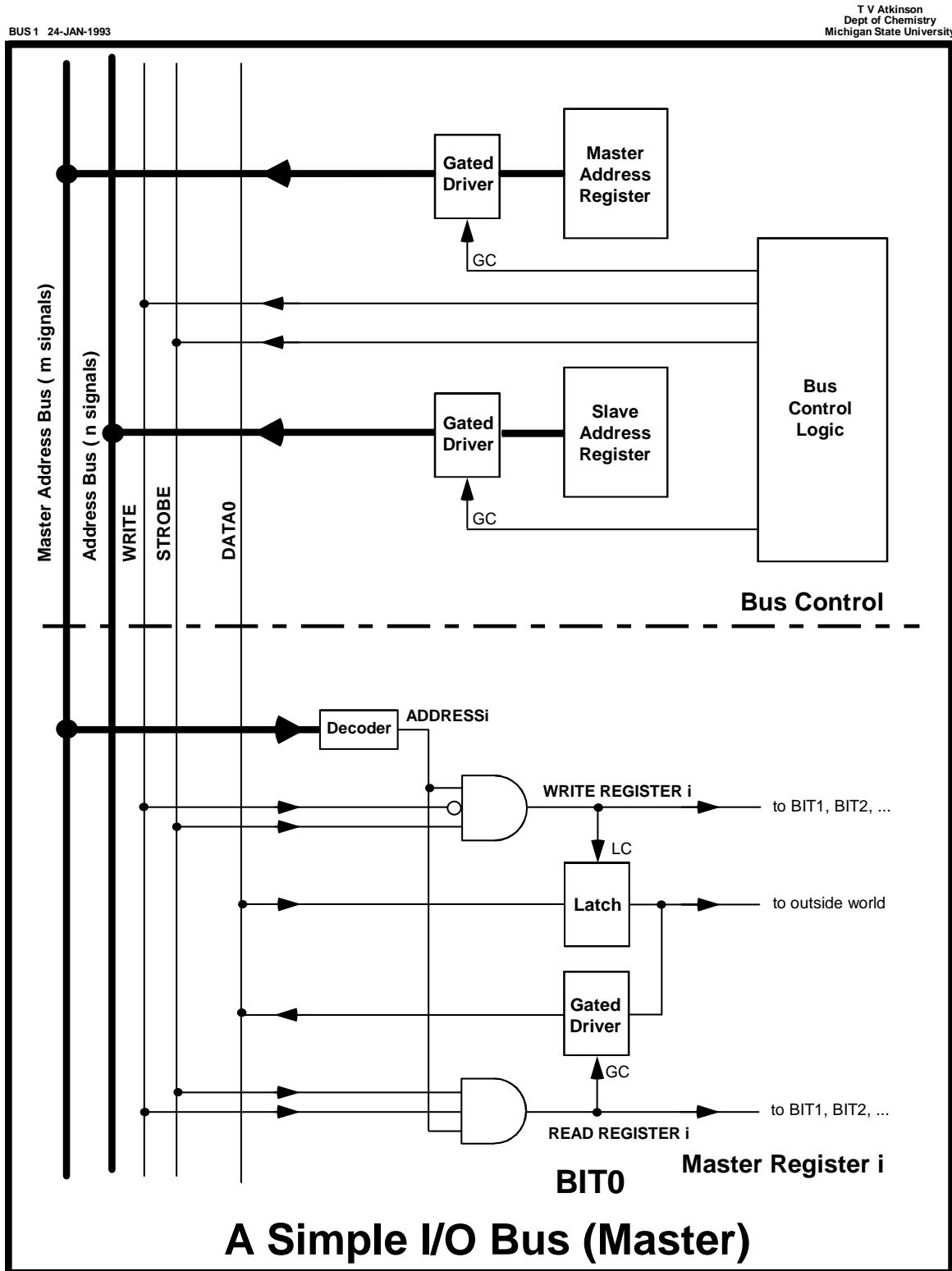

| Figure 17 Simple I/O Bus: Bus Master.....                           | 45 |

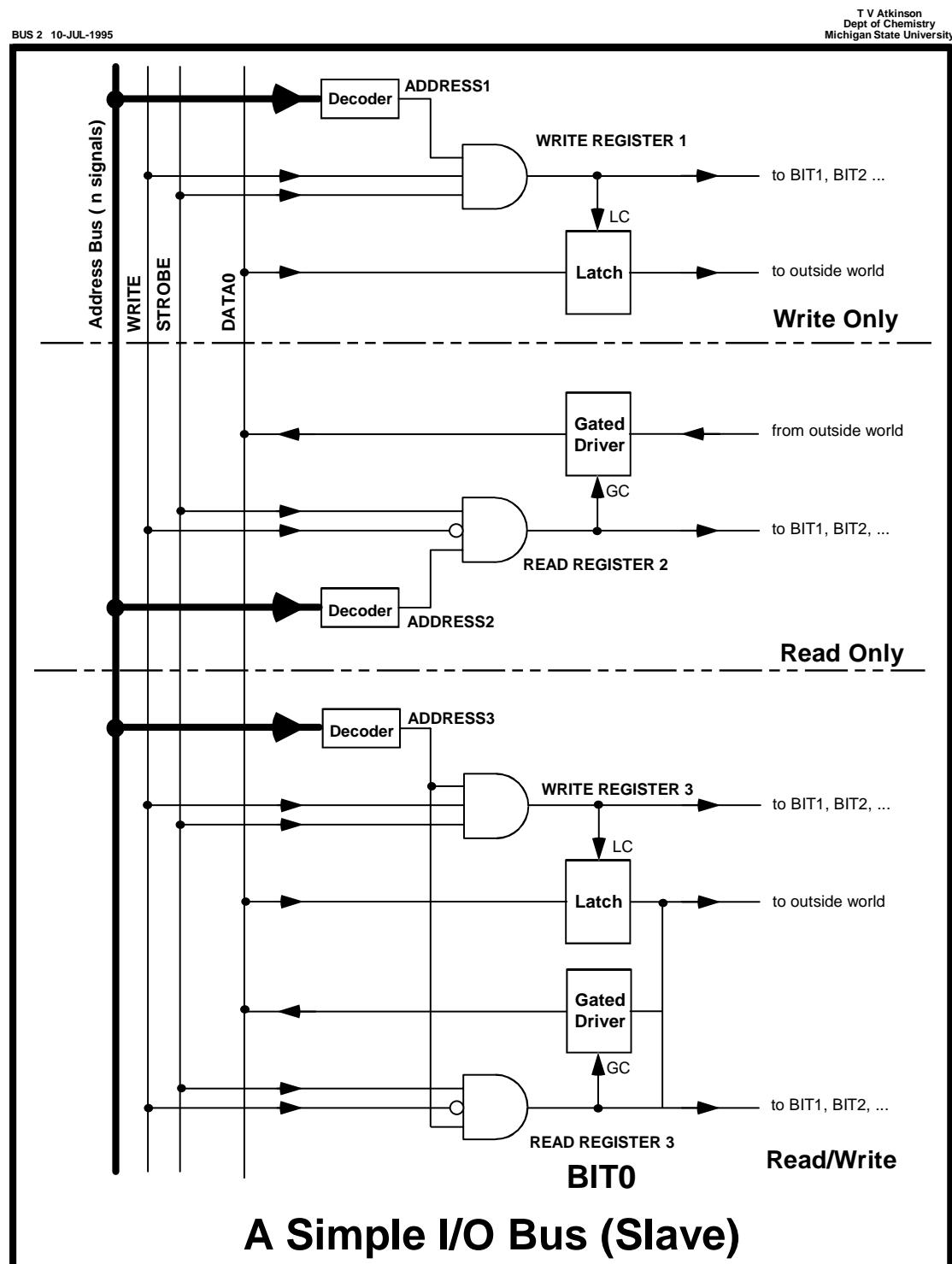

| Figure 18 Simple I/O Bus: Slave .....                               | 46 |

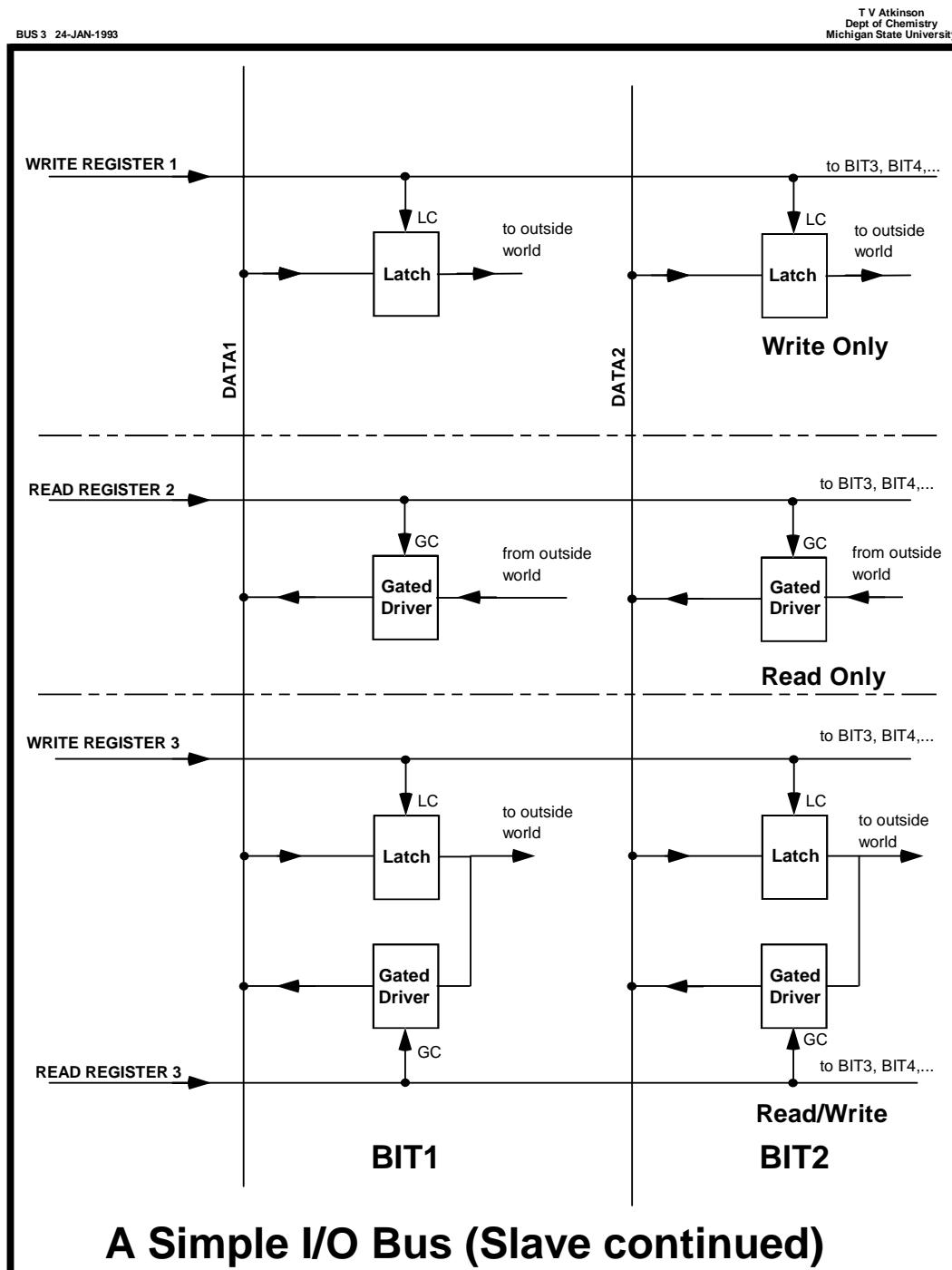

| Figure 19 Simple I/O Bus: Slave (Continued).....                    | 47 |

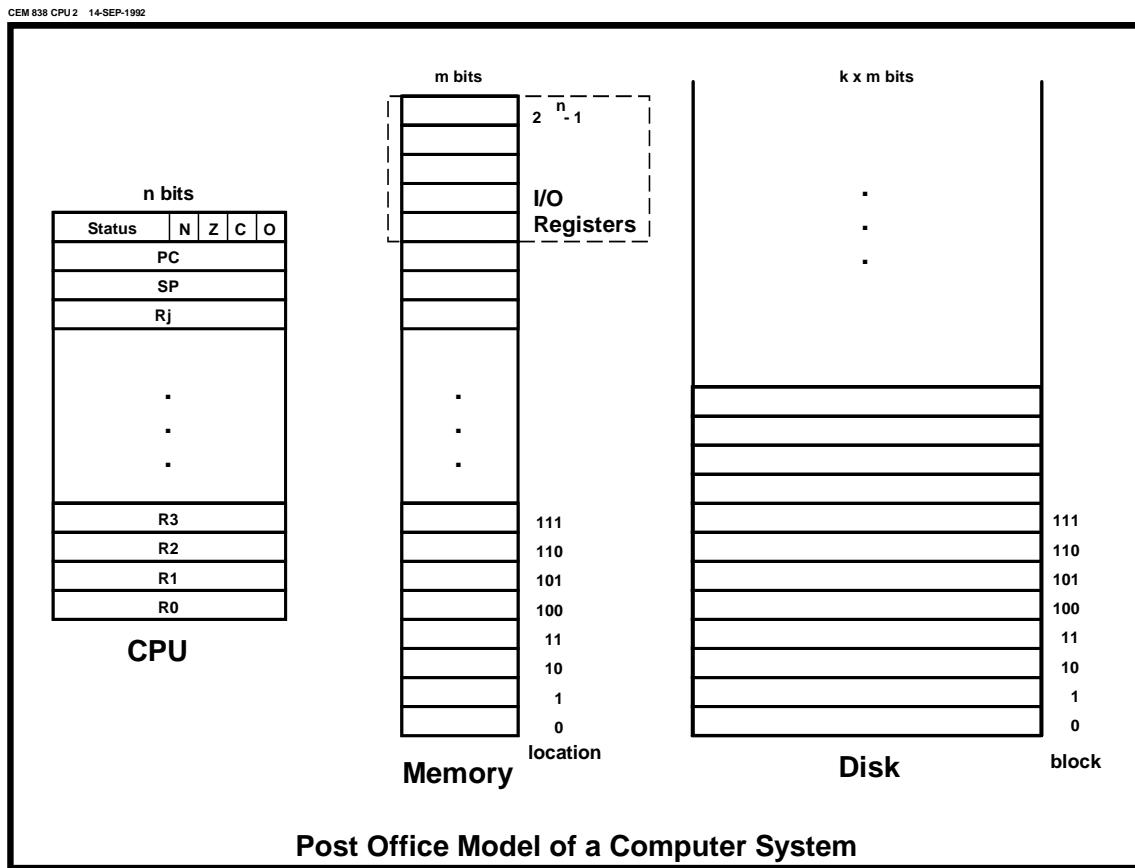

| Figure 20 Post Office Model of Computing .....                      | 50 |

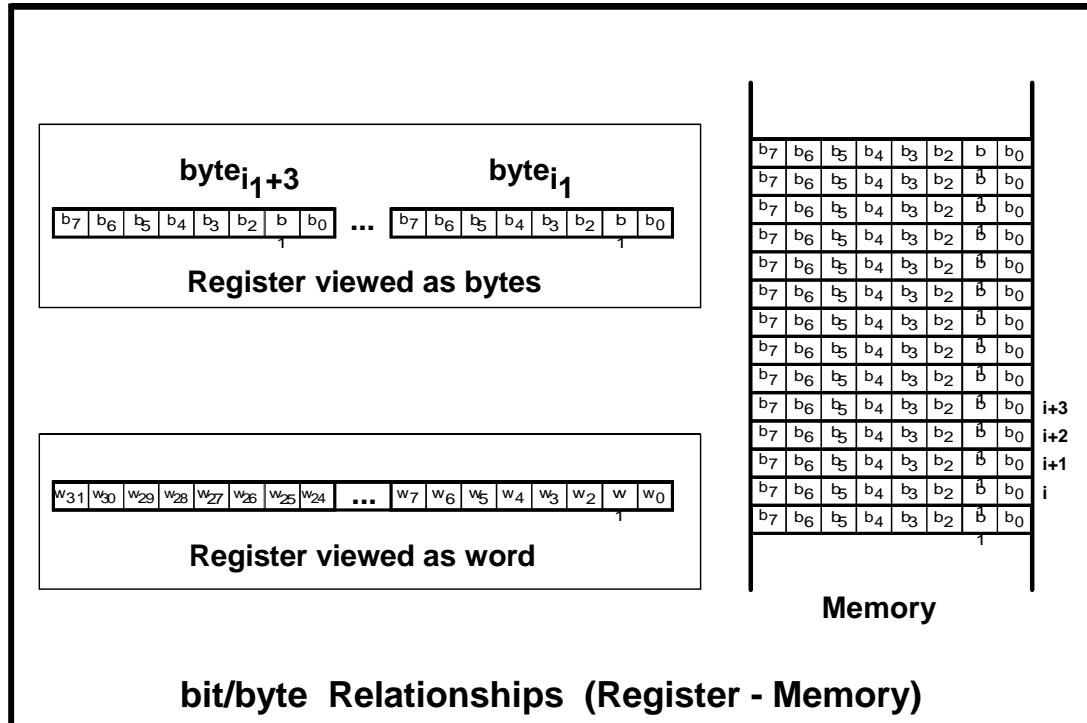

| Figure 21 Bit Byte Word Relationship .....                          | 55 |

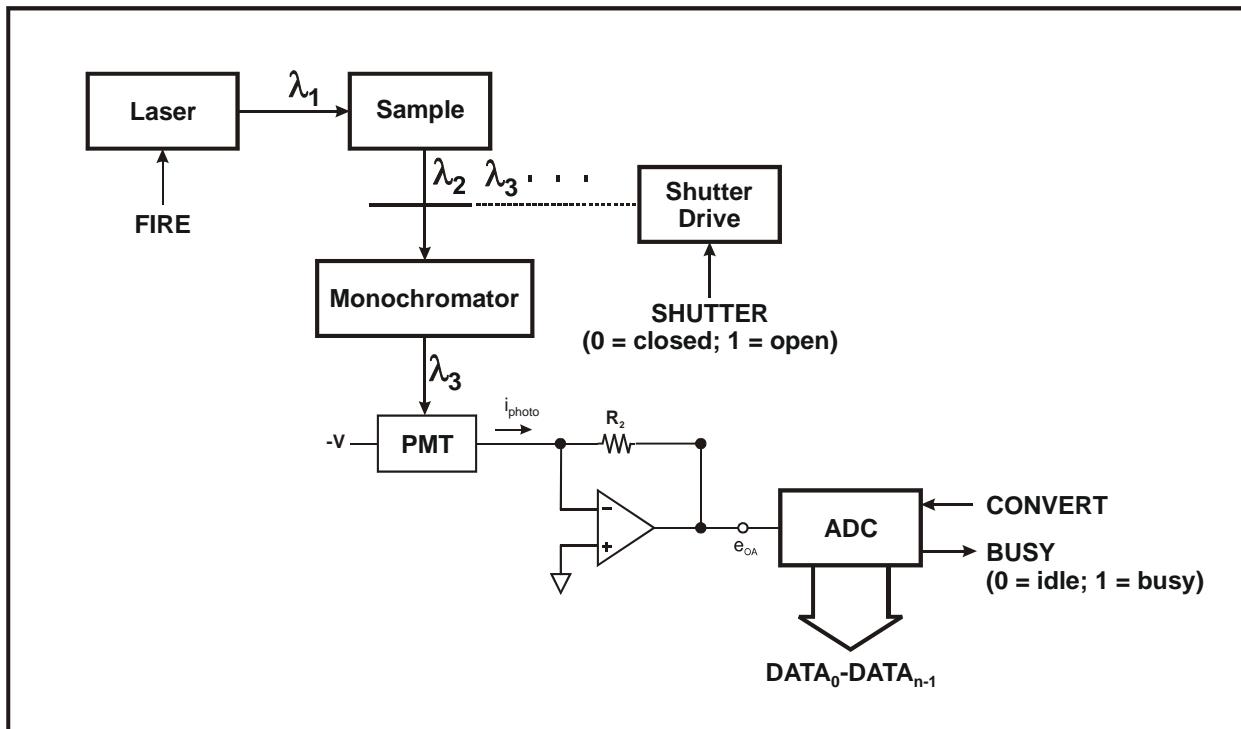

| Figure 22 Laser Experiment .....                                    | 64 |

| Figure 23 Laser Experiment Interface (software View) .....          | 66 |

| Figure 24 Laser Experiment Timing (microseconds) .....              | 71 |

| Figure 25 Special Memory Bus .....                                  | 72 |

| Figure 26 Special CPU Bus .....                                     | 73 |

| Figure 27 Floating Point CoProcessor I.....                         | 73 |

| Figure 28 Complex I/O .....                                         | 74 |

| Figure 29 Complex I/O: An Example.....                              | 75 |

| Figure 30 Multiple Processors: Very Loosely Coupled.....            | 77 |

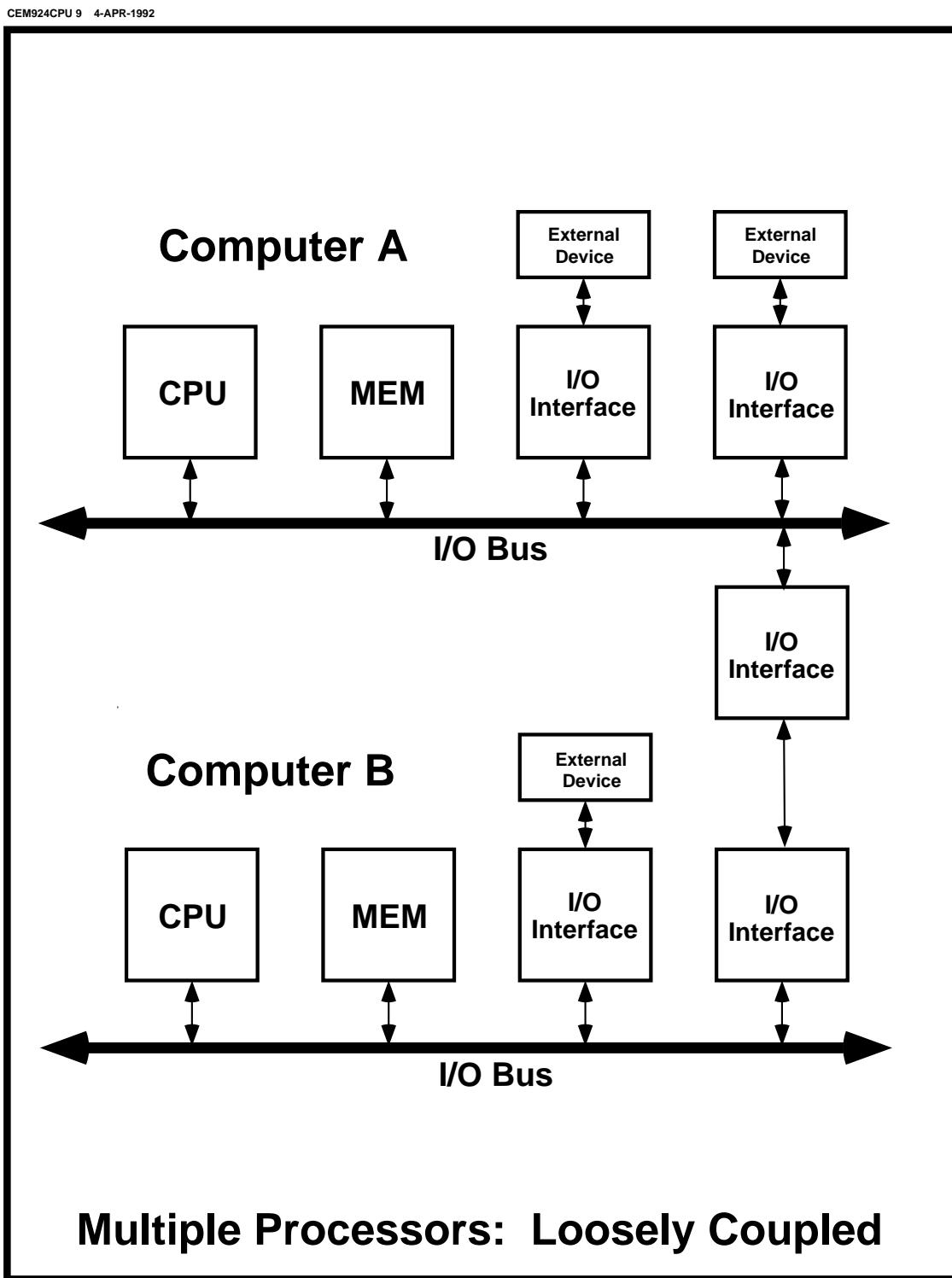

| Figure 31 Multiple Processors: Loosely Coupled.....                 | 78 |

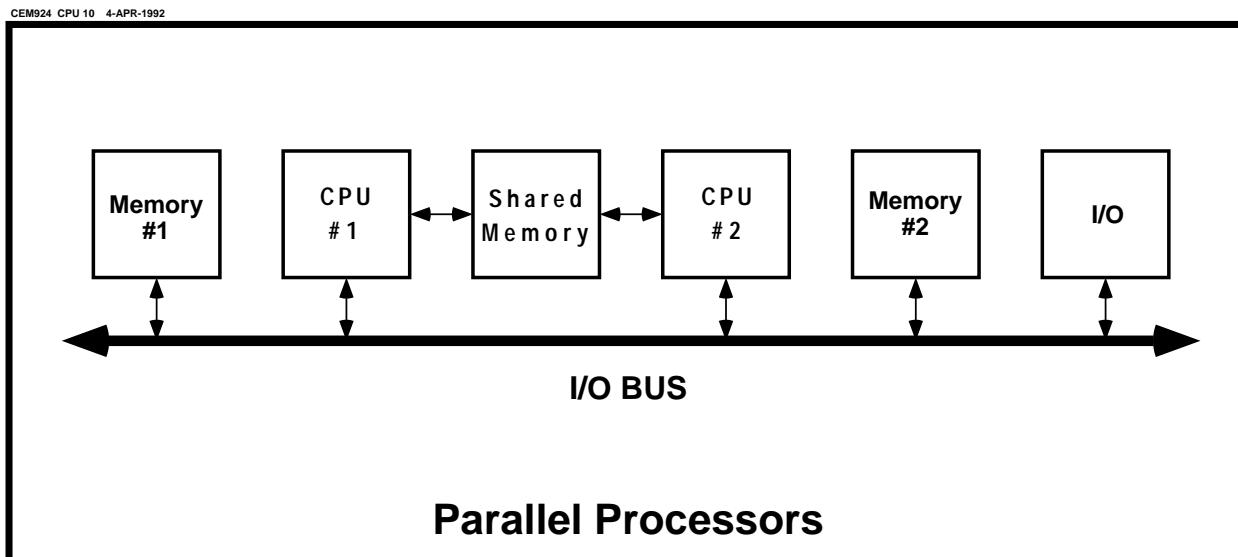

| Figure 32 Multiple Processors: Parallel.....                        | 79 |

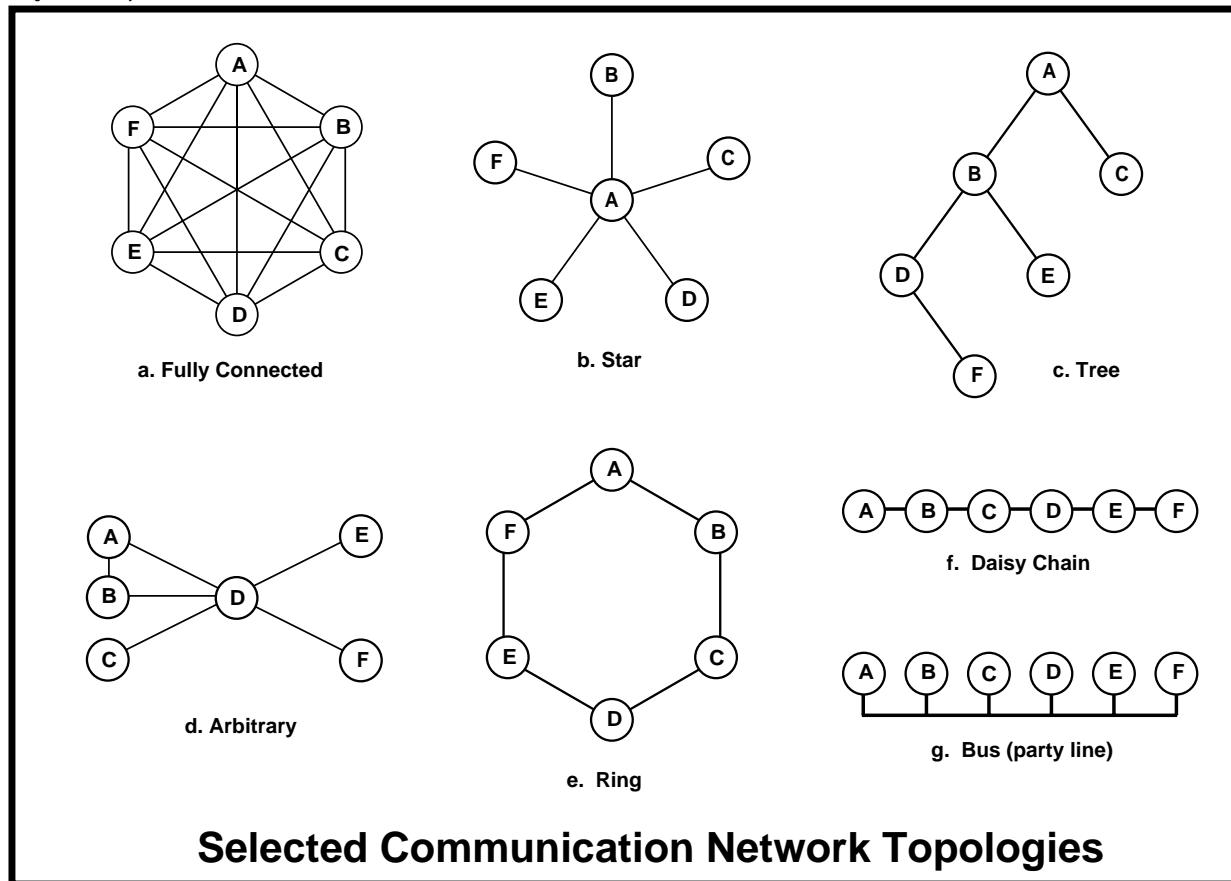

| Figure 33 Multiple Processors: Connection Topologies .....          | 79 |

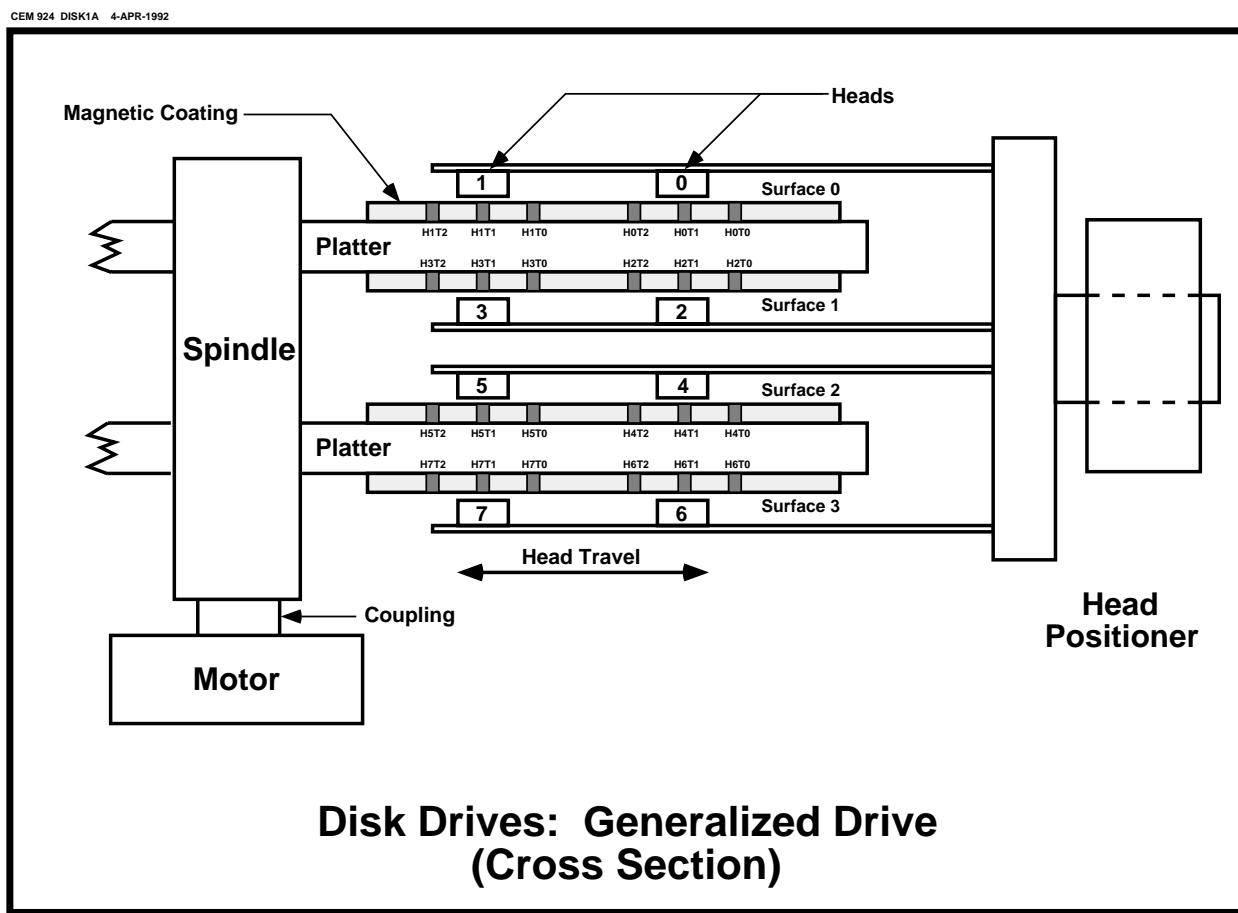

| Figure 34 Generalized Drive (Cross Section) .....                   | 80 |

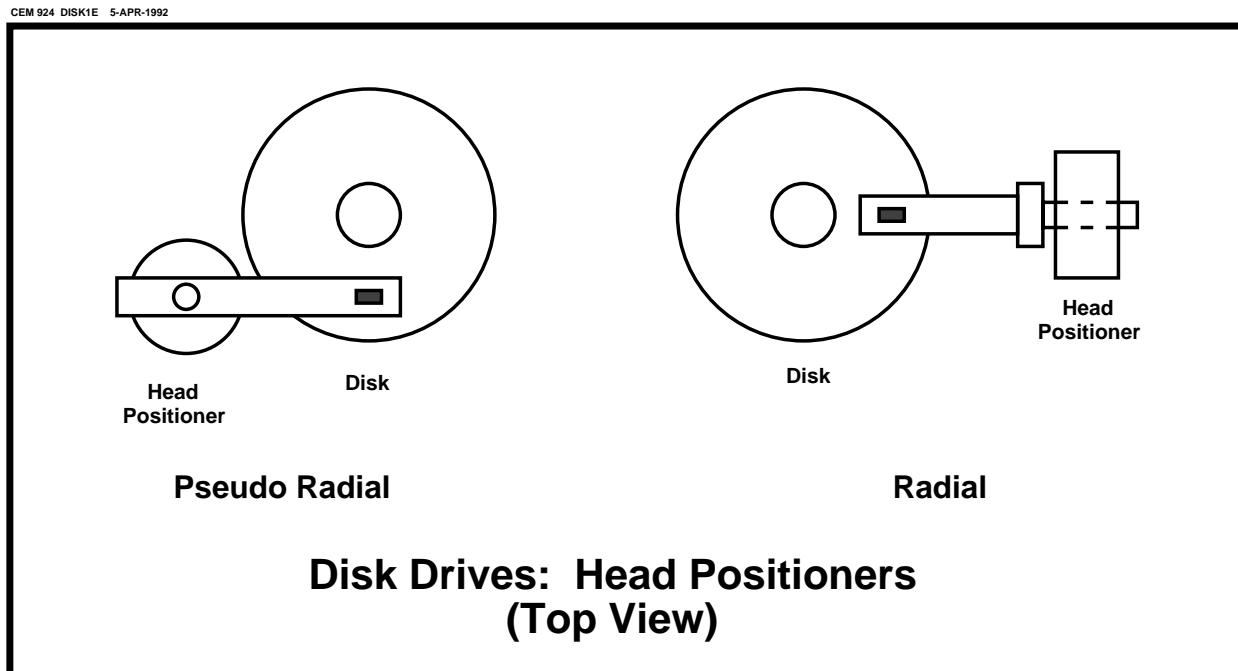

| Figure 35 Head Positioners.....                                     | 81 |

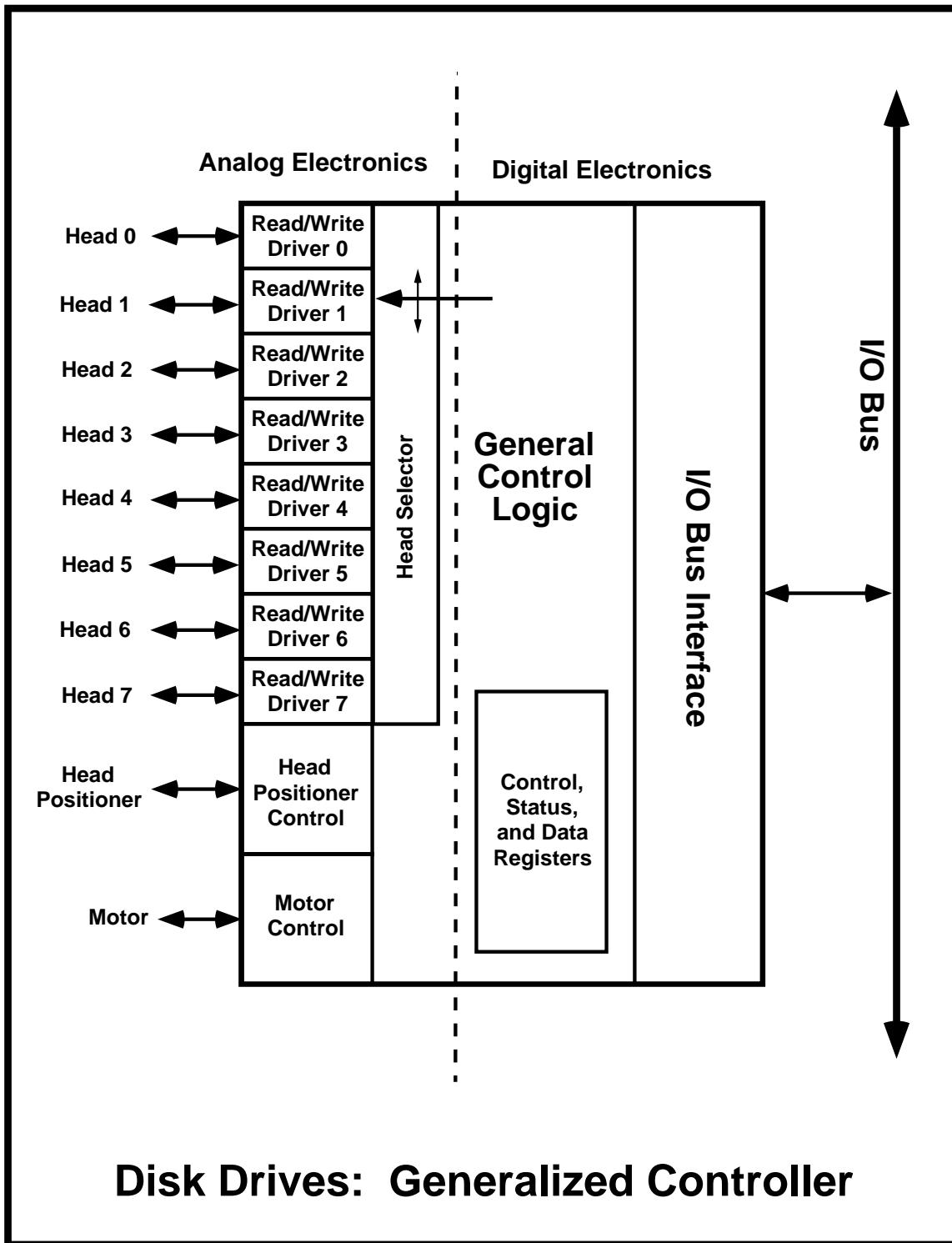

| Figure 36 Generalized Controller .....                              | 82 |

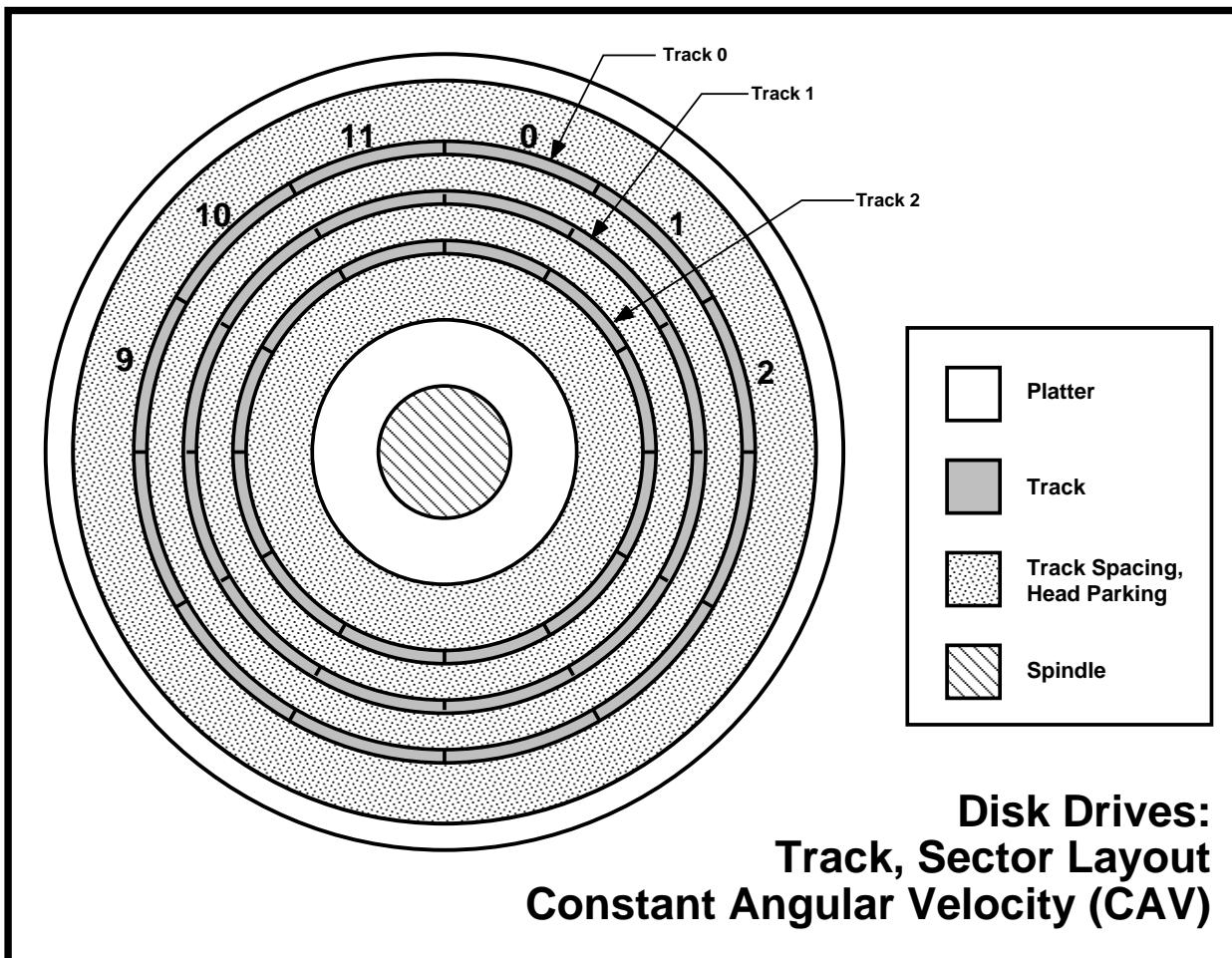

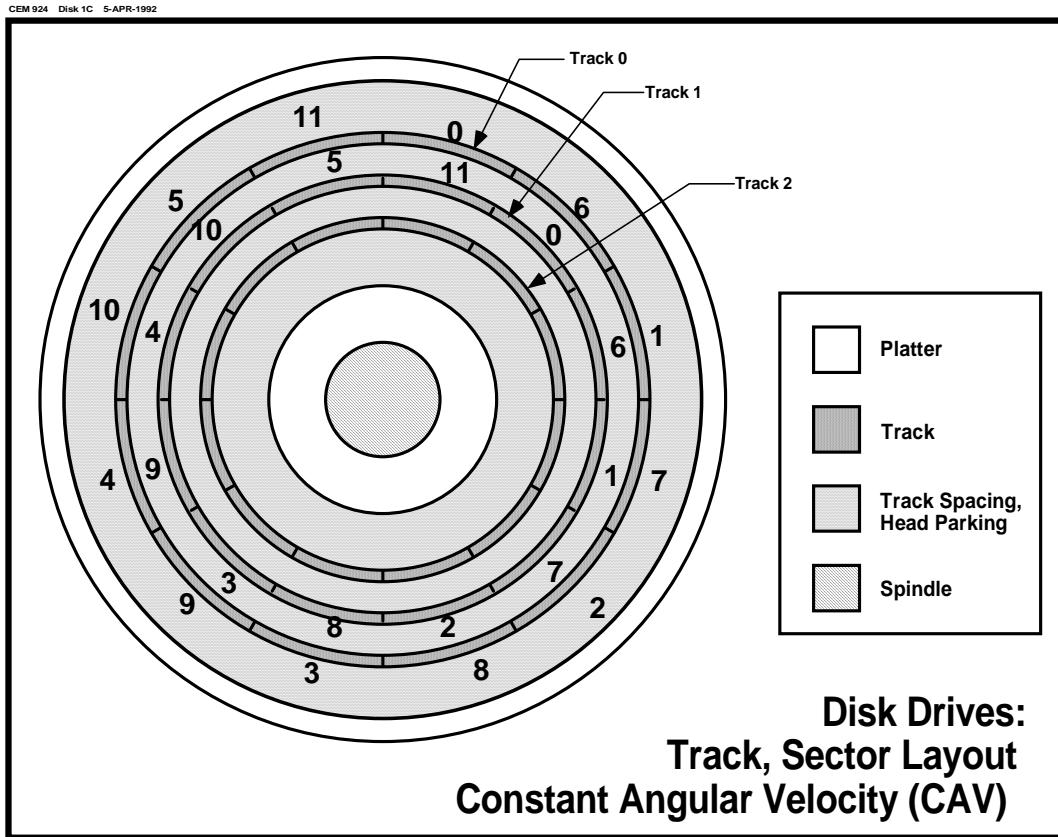

| Figure 37 Track Sector Layout: CAV.....                             | 83 |

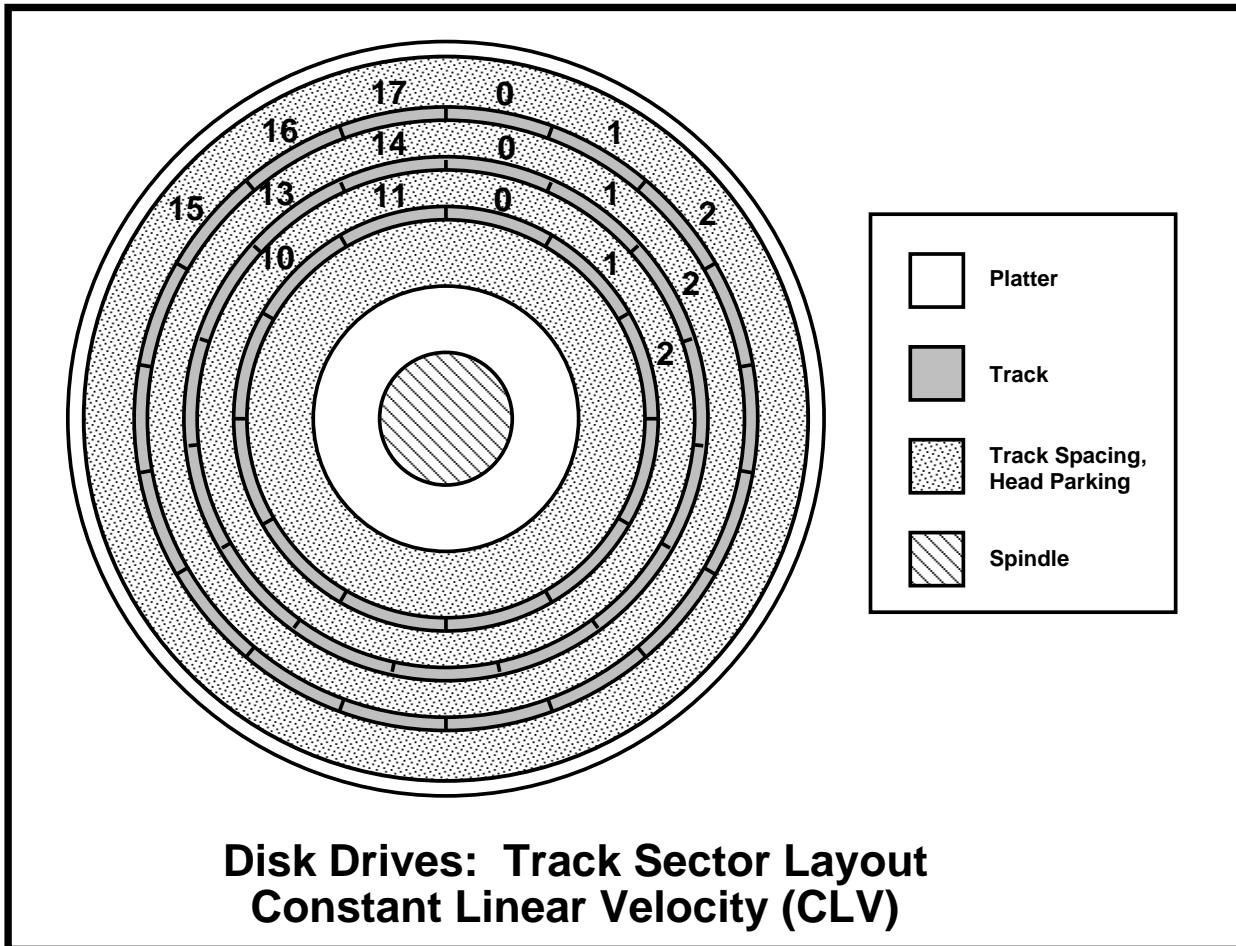

| Figure 38 Track Sector Layout: CLV .....                            | 84 |

| Figure 39 Track Skew - Interleave .....                             | 85 |

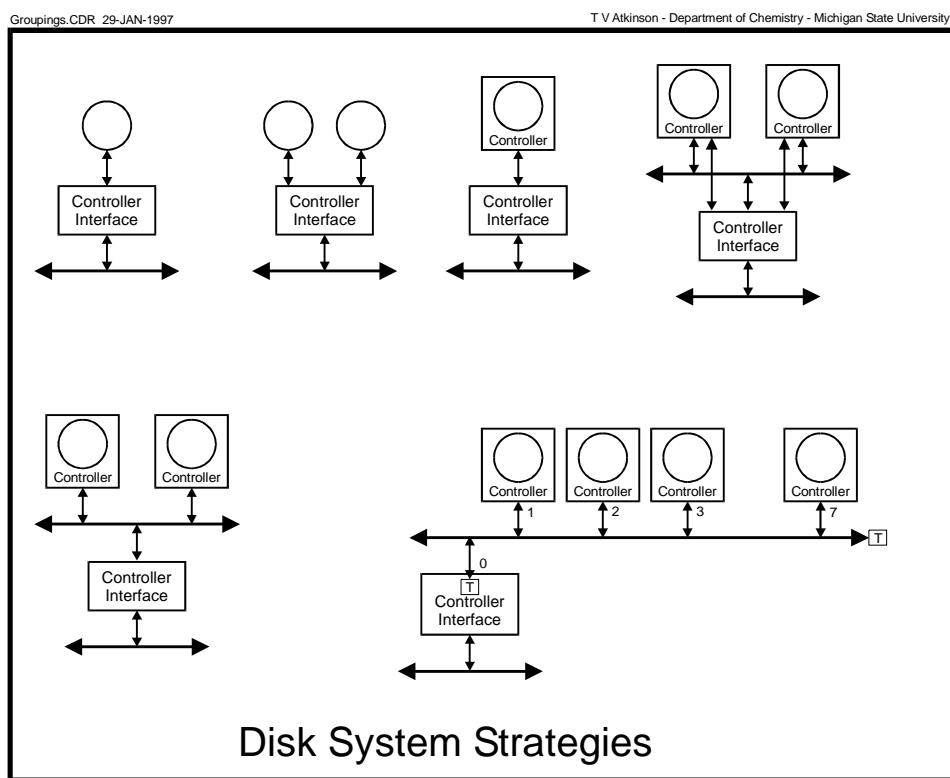

| Figure 40 Disk System Strategies .....                              | 88 |

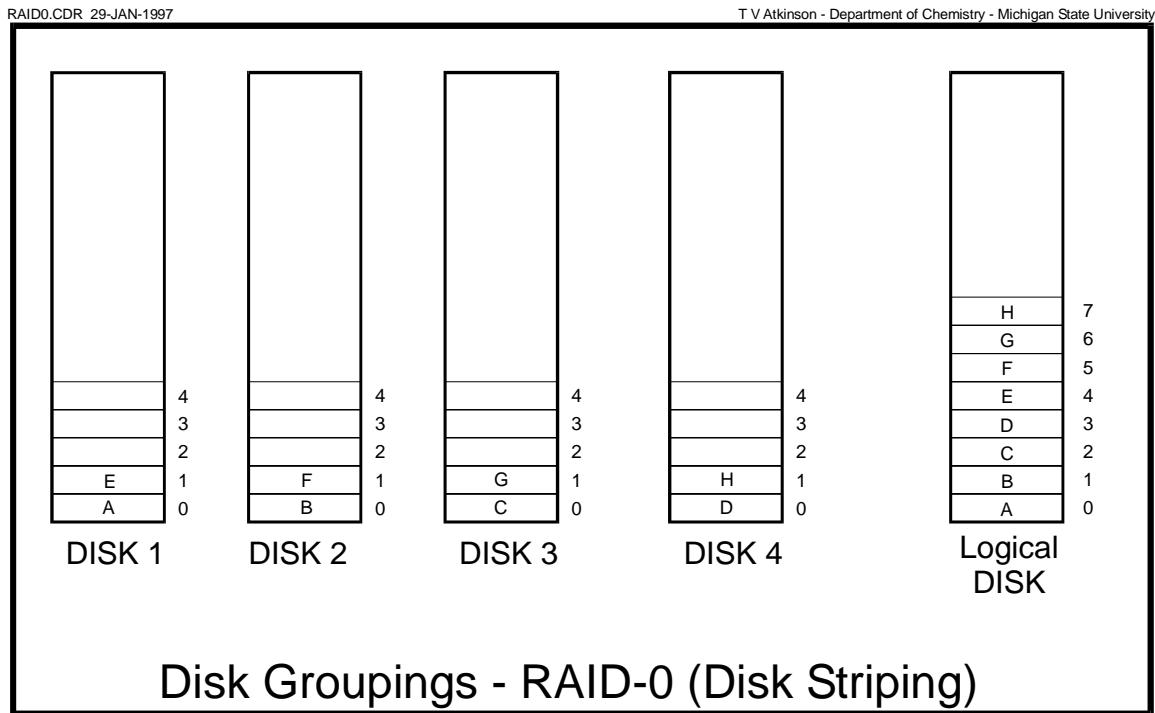

| Figure 41 Disk Groupings - Raid 0.....                              | 90 |

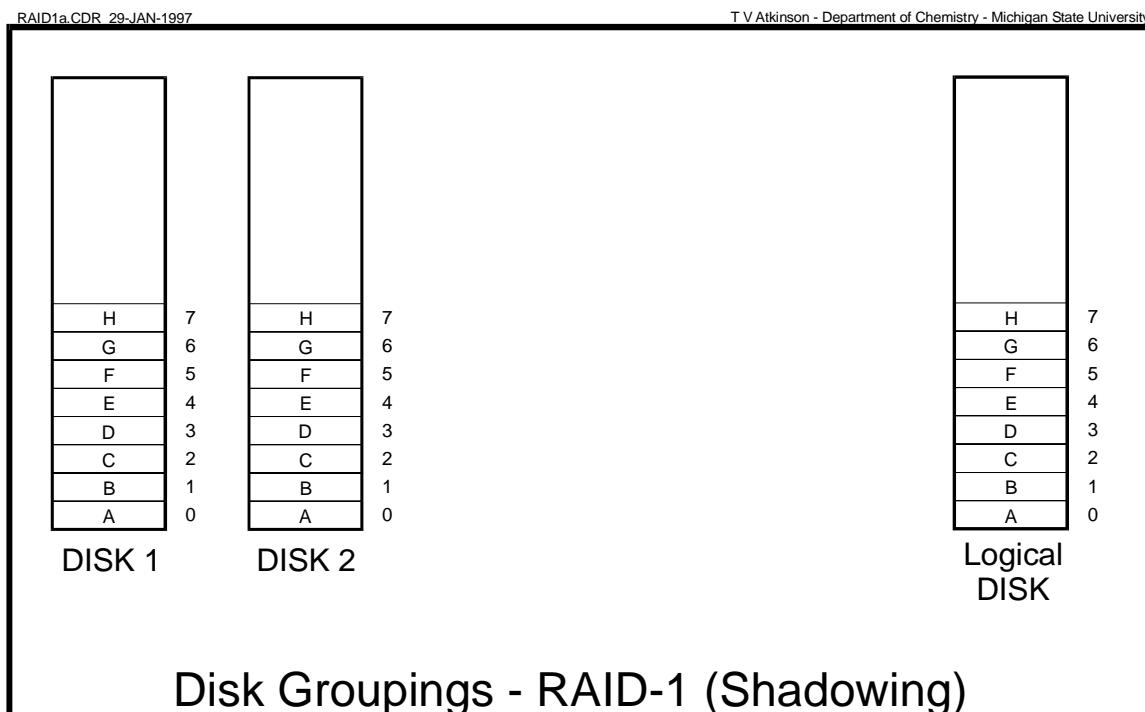

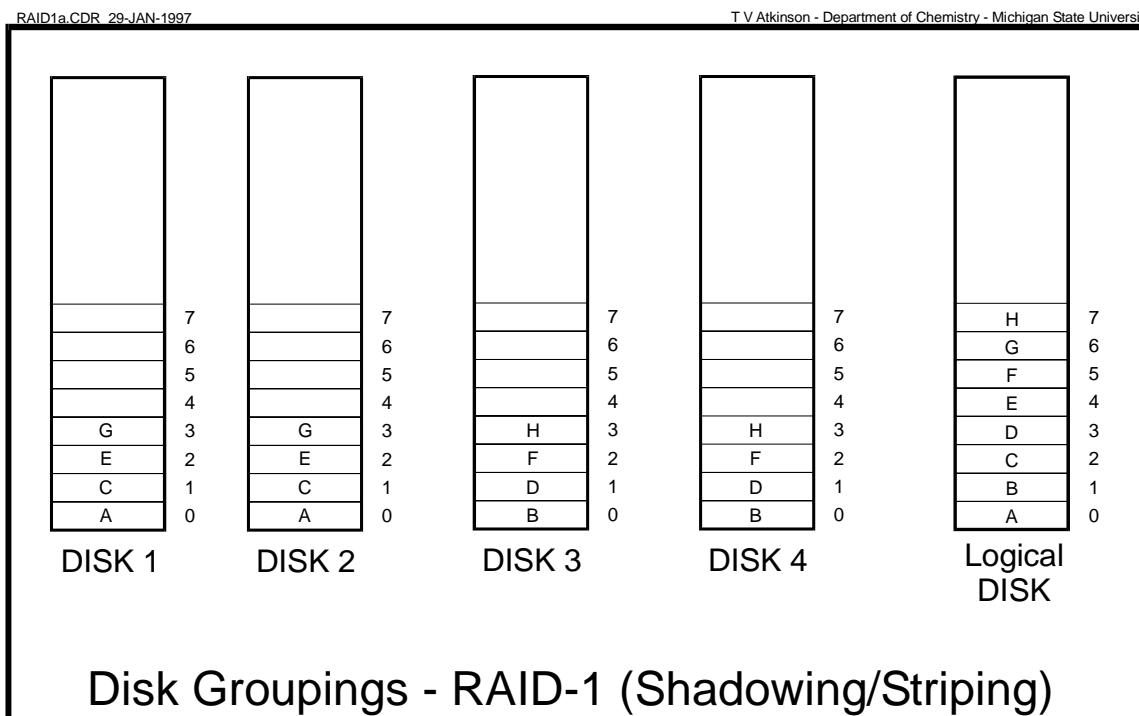

| Figure 42 Disk Groupings - Raid 1.....                              | 90 |

| Figure 43 Disk Groupings - Raid 1 Alternative.....                  | 91 |

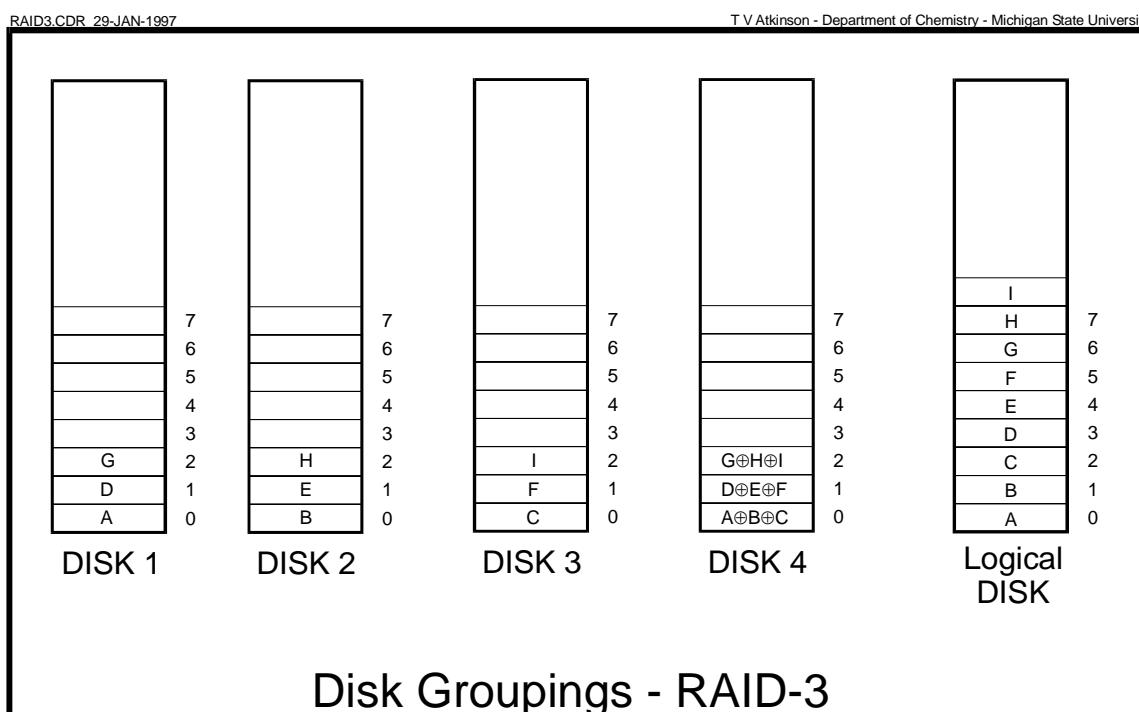

| Figure 44 Disk Groupings - Raid 3.....                              | 91 |

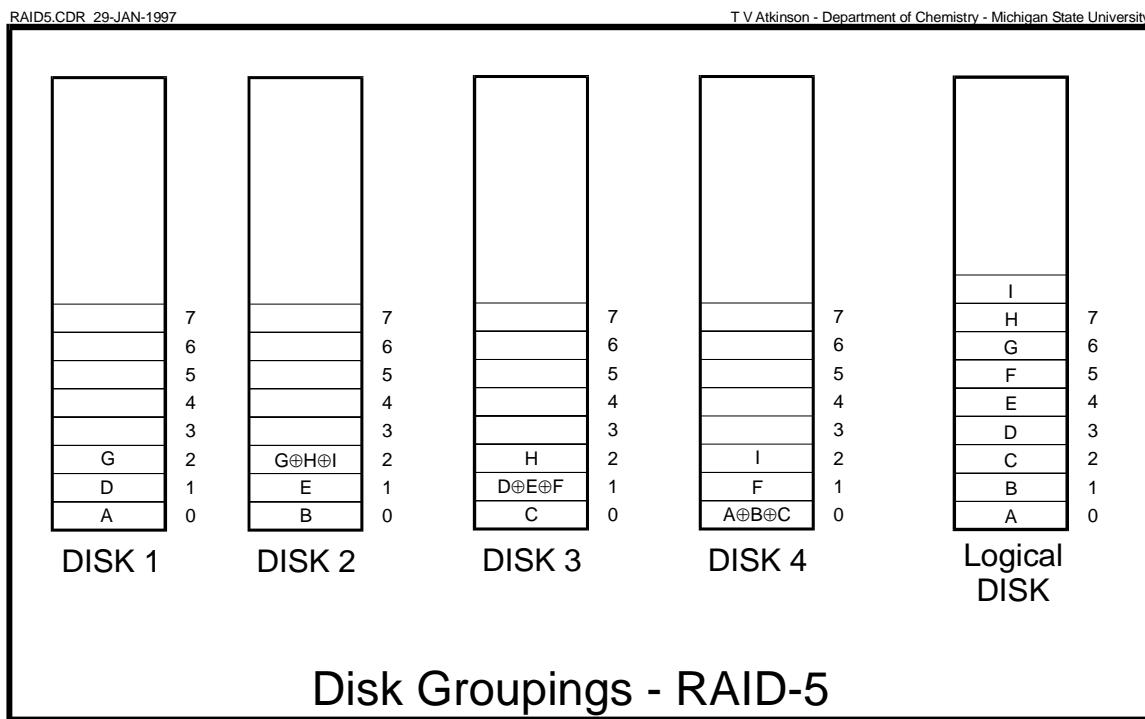

| Figure 45 Disk Groupings - Raid 5.....                              | 92 |

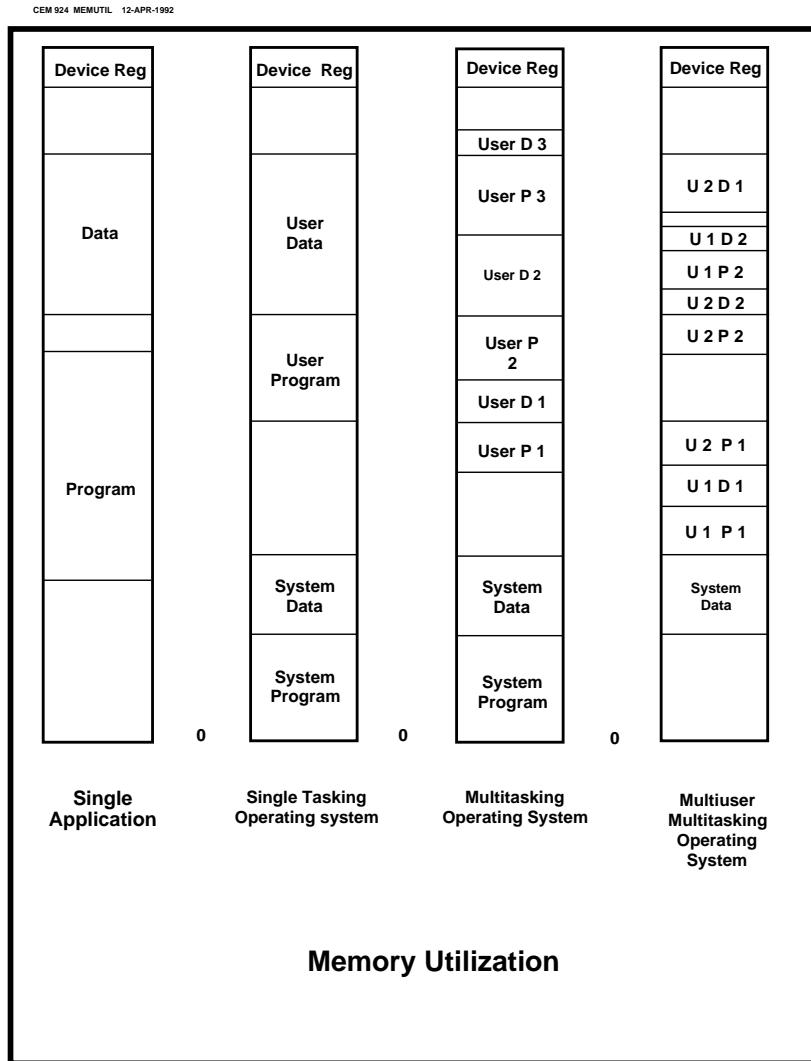

| Figure 46 Memory Utilization .....                                  | 93 |

| Figure 47 Boot Strapping.....                                       | 94 |

| Figure 48 Front Panel Emulator.....                                 | 96 |

| Figure 49 Booting a ROM Based OS .....                              | 97 |

## Aspects of Computer Architecture

|                                                         |     |

|---------------------------------------------------------|-----|

| Figure 50 Concurrent Tasks.....                         | 102 |

| Figure 51 Concurrent Tasks (Partial Dependence).....    | 103 |

| Figure 52 Cache and RAM Disk.....                       | 104 |

| Figure 53 Memory Cache Controller.....                  | 104 |

| Figure 54 Program I/O .....                             | 106 |

| Figure 55 DMA Example.....                              | 109 |

| Figure 56 Program Exceeds Memory Available.....         | 111 |

| Figure 57 Memory Limited Programming (Chaining) .....   | 113 |

| Figure 58 Memory Limited Programming (Overlaying) ..... | 114 |

| Figure 59 Overlaying (Memory Layout) .....              | 115 |

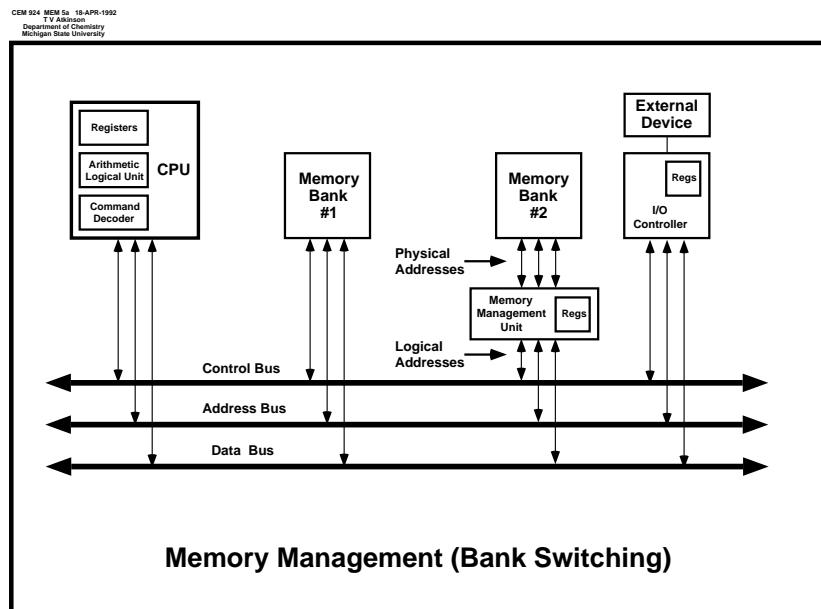

| Figure 60 Memory Management .....                       | 116 |

| Figure 61 Bank Switching: Mapping.....                  | 117 |

| Figure 62 Bank Switching: Memory Space .....            | 118 |

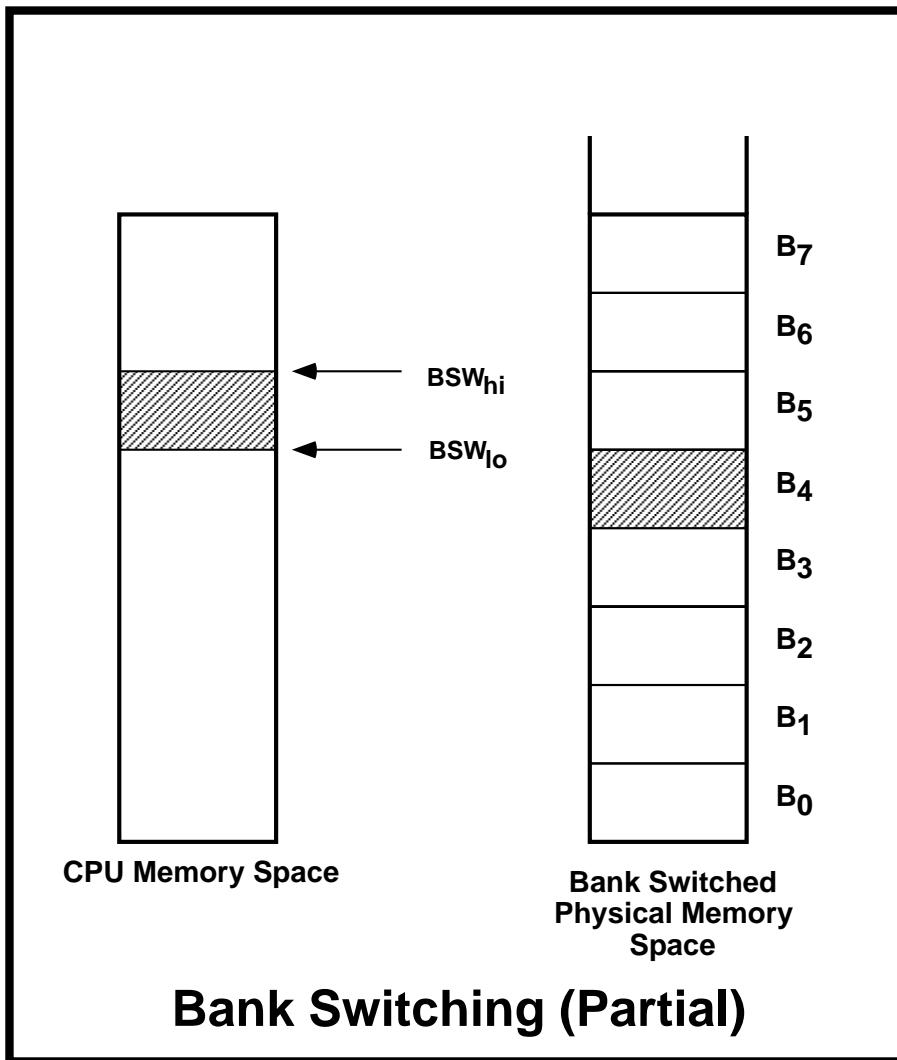

| Figure 63 Bank Switching (Partial) .....                | 119 |

| Figure 64 Bank Switching (Partial): Memory Spaces ..... | 120 |

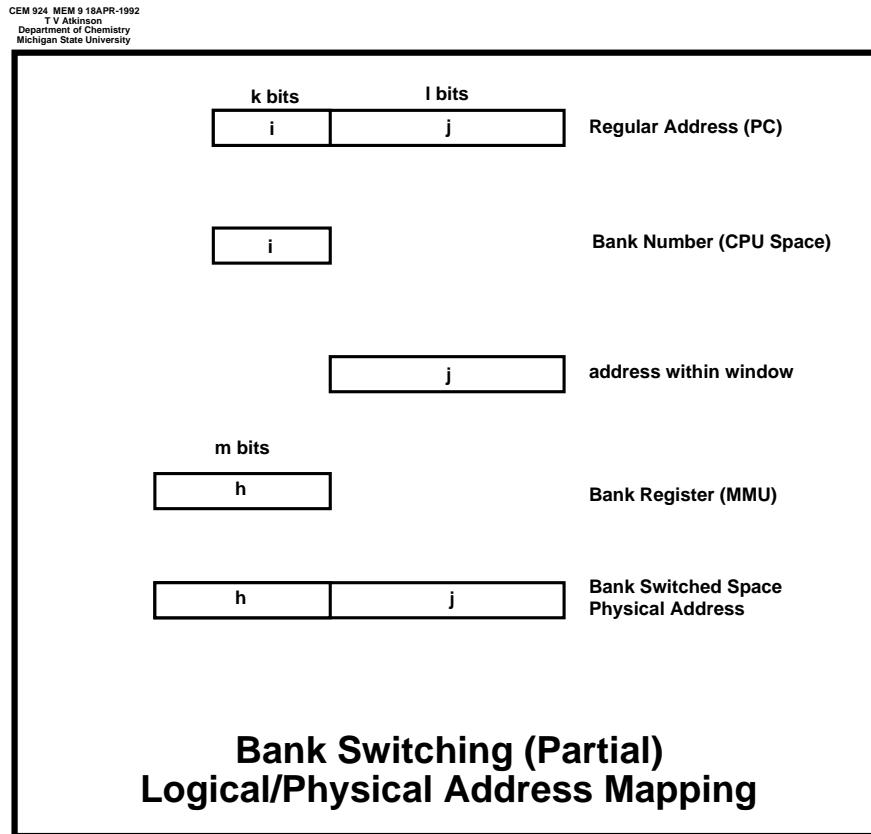

| Figure 65 Bank Switching(Partial): Mapping.....         | 121 |

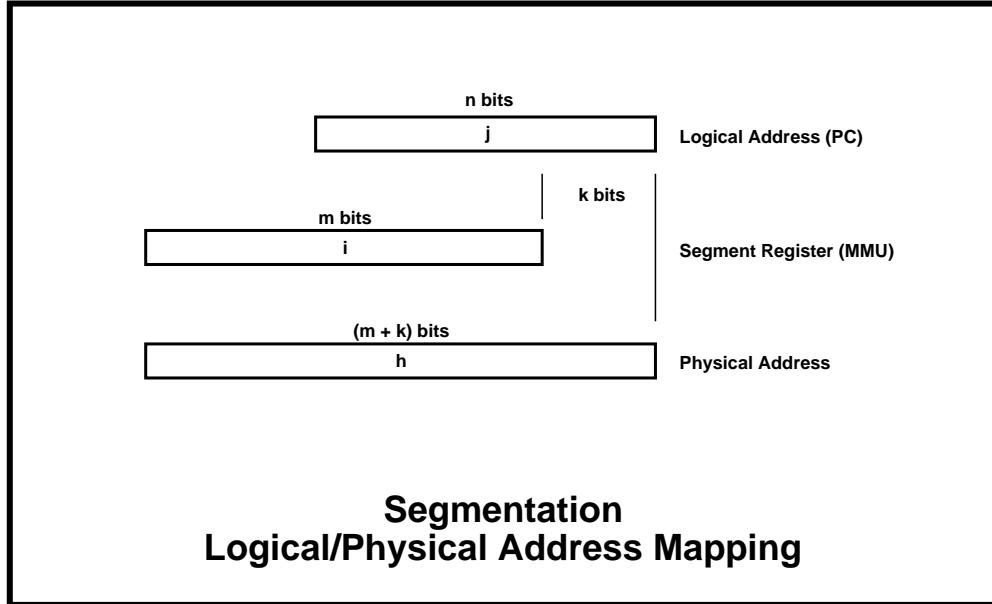

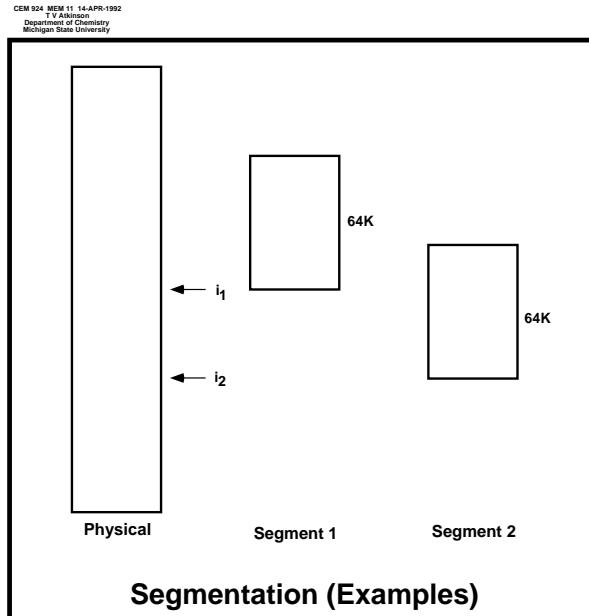

| Figure 66 Segmentation: Mapping .....                   | 122 |

| Figure 67 Segmentation: Memory Spaces .....             | 123 |

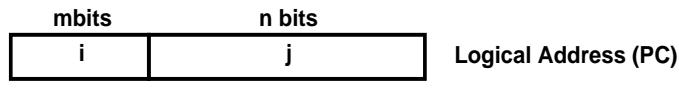

| Figure 68 Paging: Mapping .....                         | 124 |

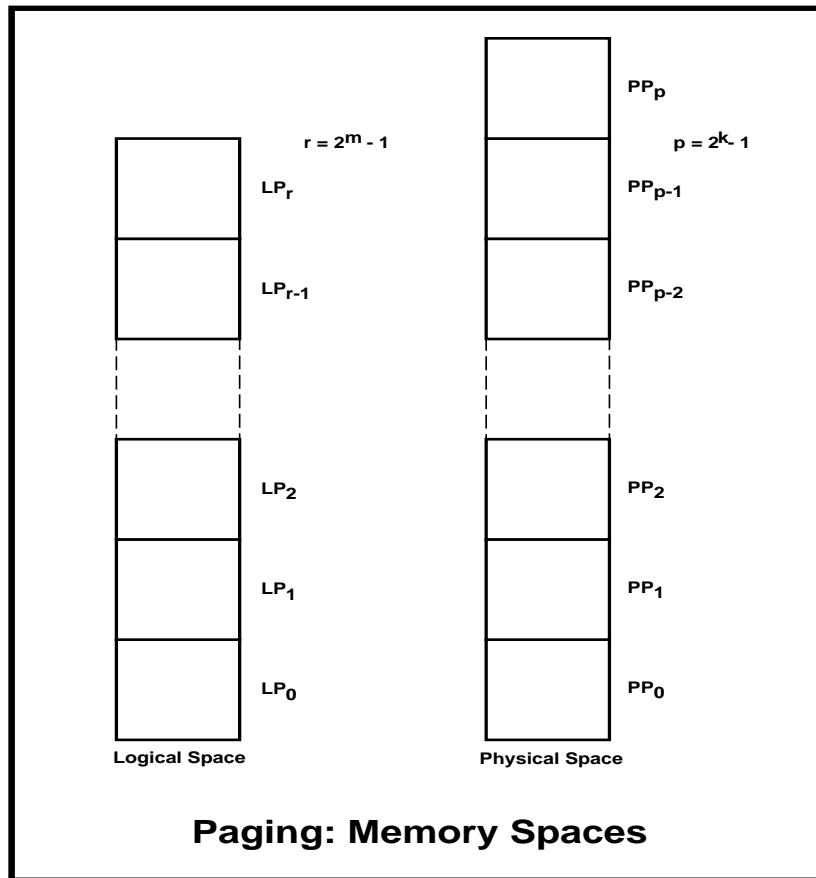

| Figure 69 Paging: Memory Spaces .....                   | 125 |

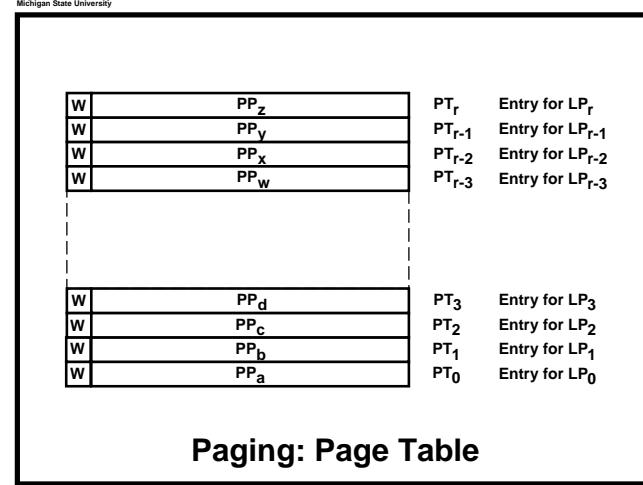

| Figure 70 Paging: Page Table .....                      | 125 |

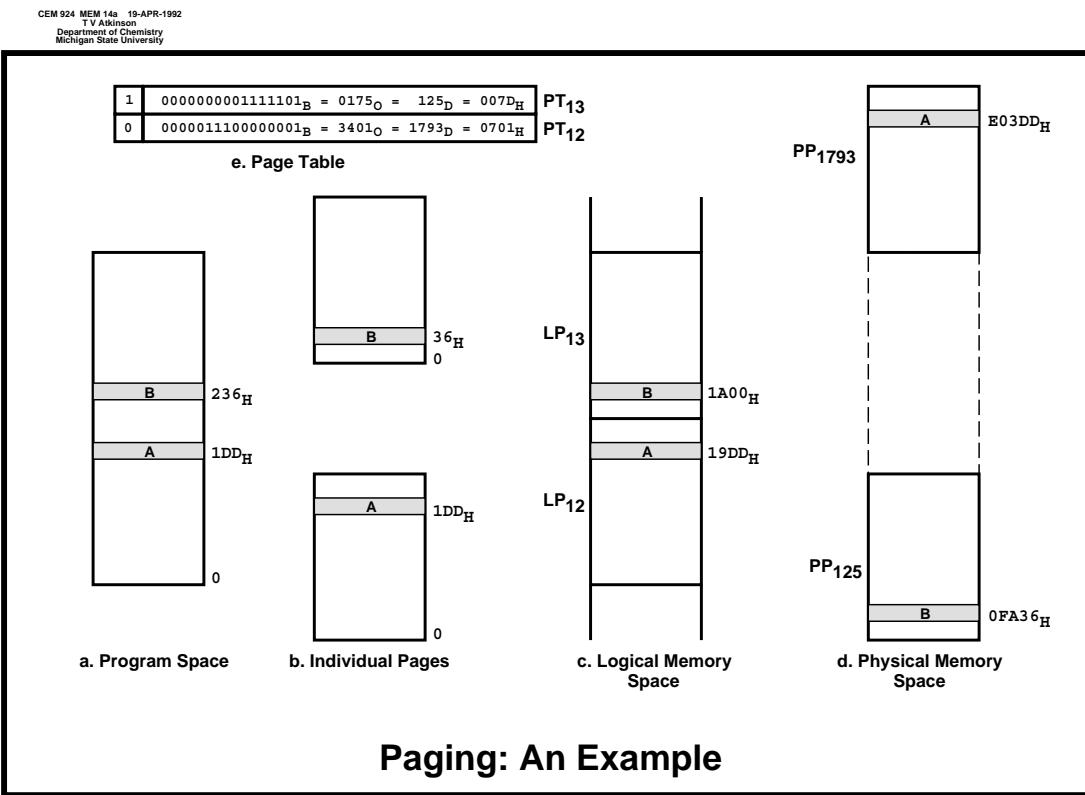

| Figure 71 Paging: An Example.....                       | 128 |

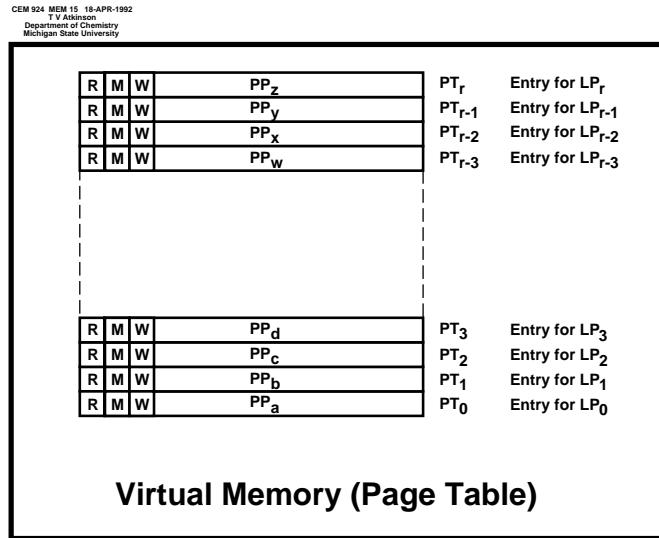

| Figure 72 Virtual Memory: Page Table .....              | 129 |

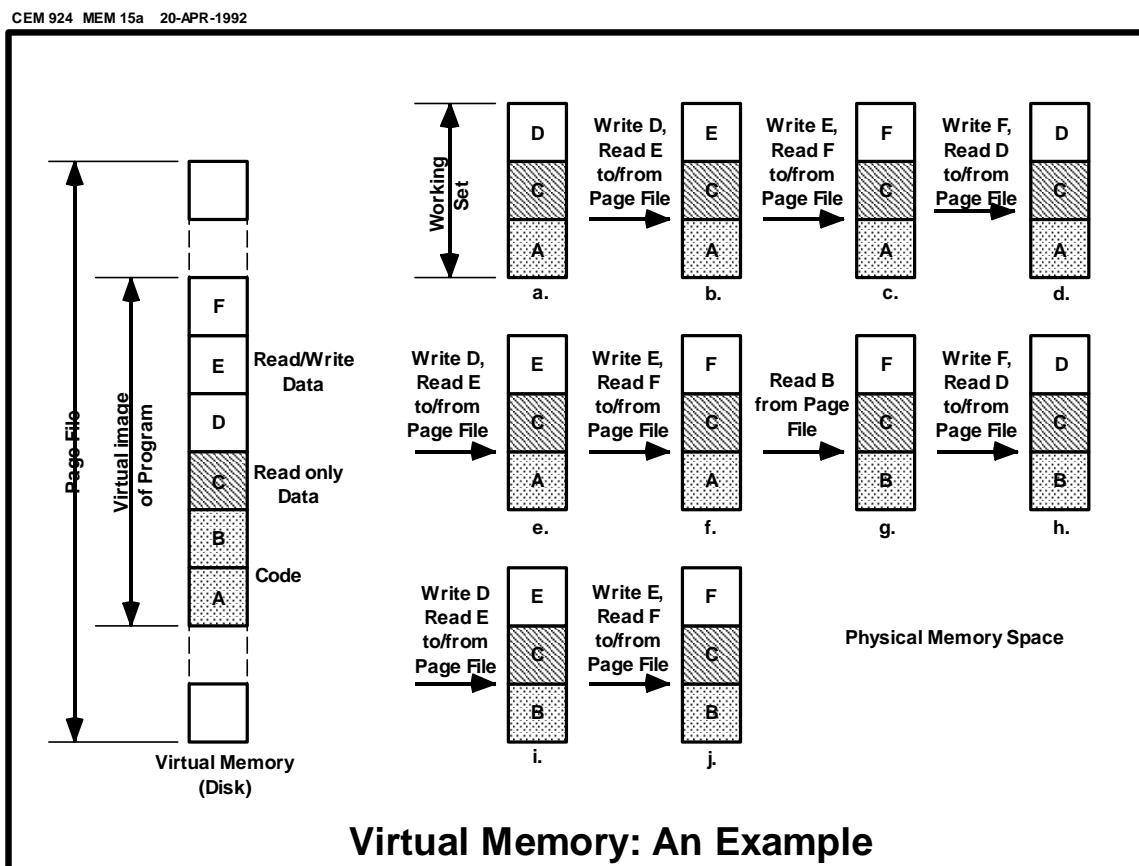

| Figure 73 Virtual Memory: An Example.....               | 130 |

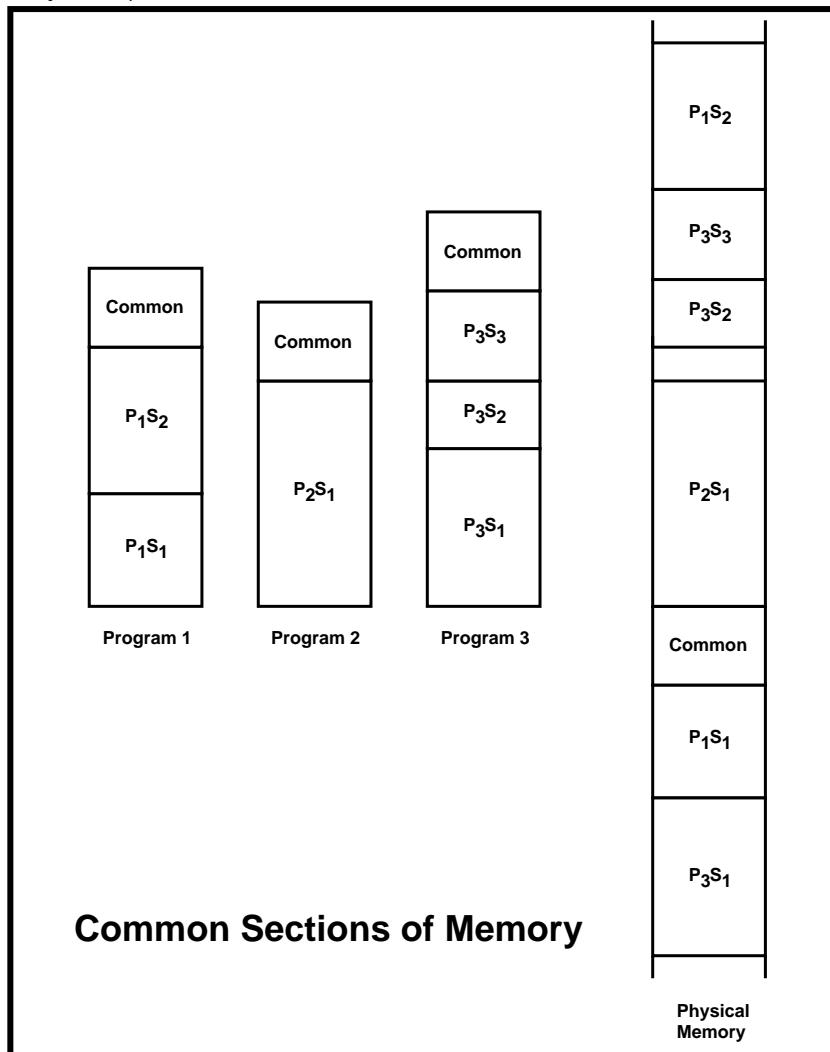

| Figure 74 Common Sections.....                          | 132 |

| Figure 75 Memory Protection.....                        | 133 |

# Aspects of Computer Architecture

## Introduction

### 1. Introduction

#### 1.1. Why should Chemists care about this material?

1. Typically, the chemistry professionals will encounter many different computer environments during their careers.

2. We (want to, need to, have to) use computers to do our work and have fun.

#### 1.2. How can we characterize the people who use computers?

##### 1.2.1. By the Type of Use

1. Application user

2. Operator

3. System manager

4. Application programmer

5. System programmer

6. Hardware developer

7. Software maintainer

8. Hardware maintainer

9. Hardware and software documentor

10. User support

##### 1.2.2. By frequency of use of a particular program or facility

1. Occasional

2. Frequent

##### 1.2.3. By level of expertise for a given program or facility

1. Novice

2. Versed

3. Expert/wizard/guru

## Aspects of Computer Architecture

### Number Systems

#### 2. Number Systems

An integer is represented in our system of writing by a string of symbols, digits, ( $d_i$ ) from the set  $\{0, 1, 2, \dots, b-1\}$  as shown below where "b" is the base of the representation.

$$\text{number} \Rightarrow d_n d_{n-1} \cdots d_2 d_1 d_0 b$$

Numerically, the above notation represents the following sum.

$$\text{number} = \sum_{i=0}^n d_i \cdot b^i$$

As an example, the following are different representations of the same number.

$$\text{number} = 1010001110110010_2 = 121662_8 = 41906_{10} = A3B2_{16}$$

Fractional numbers can also be represented.

$$\text{number} \Rightarrow d_{-1} d_{-2} \cdots d_{-m+1} d_{-m}$$

$$\text{number} = \sum_{i=-1}^{-m} d_i b^i$$

The following are different representations of the same numbers.

$$\text{number} = 0.1_2 = 0.4_8 = 0.5_{10} = 0.8_{16}$$

$$\text{number} = 0.01_2 = 0.2_8 = 0.25_{10} = 0.4_{16}$$

$$\text{number} = 0.11_2 = 0.7_8 = 0.75_{10} = 0.C_{16}$$

The general notation is as follows where "s" is the sign of the number and may be thought of as being either +1 or -1.

$$\text{number} \Rightarrow s d_2 d_1 d_0 . d_{-1} d_{-2} \cdots d_{-m+1} d_{-m}$$

$$\text{number} = s \cdot \sum_{i=n}^{-m} d_i \cdot b^i$$

Scientific notation can be generalized as follows. In the following " $s_m$ " is the sign of the mantissa, " $s_e$ " is the sign of the exponent, and "B" is a symbol characteristic of the base.

$$\text{number} \Rightarrow s d_2 d_1 d_0 . d_{-1} d_{-2} \cdots d_{-m+1} d_{-m} B s_e e_n e_{n-1} \cdots e_2 e_1 e_0$$

$$\text{number} = \left( s_m \cdot \sum_{i=-m}^n d_i \cdot b^i \right) \cdot \left( b^{s_e} \cdot \sum_{j=0}^n e_j \cdot b^j \right)$$

## Aspects of Computer Architecture

### Number Systems

#### 2.1. Range of Numbers

A given modulus,  $b$ , and a fixed number,  $n$ , of digits can express  $b^n$  numbers that range from 0 to  $b^n - 1$ . For example, in base 10, 5 digits can represent 100000 numbers from 0 to 99999. For base 2, 16 digits can represent 65536 ( $2^{16}$ ) numbers from 0 to 65535.

#### 2.2. Converting Between Different Moduli

Conversion of a number from one power of two modulus to another power of two modulus is fairly simple and very useful. The following discussion will assume unsigned integers that can be expressed in 16 binary digits (bits).

$$\text{number} \Rightarrow b_{15} b_{14} b_{13} b_{12} b_{11} b_{10} b_9 b_8 b_7 b_6 b_5 b_4 b_3 b_2 b_1 b_0$$

$$\begin{aligned} \text{number} = & b_{15} \cdot 2^{15} + b_{14} \cdot 2^{14} + b_{13} \cdot 2^{13} + b_{12} \cdot 2^{12} + b_{11} \cdot 2^{11} + b_{10} \cdot 2^{10} + b_9 \cdot 2^9 + b_8 \cdot 2^8 \\ & + b_7 \cdot 2^7 + b_6 \cdot 2^6 + b_5 \cdot 2^5 + b_4 \cdot 2^4 + b_3 \cdot 2^3 + b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0 \end{aligned}$$

##### 2.2.1. Binary to/from Hexadecimal

Notice that the terms can be grouped in subsets of 4 as follows.

$$\begin{aligned} \text{number} = & (b_{15} \cdot 2^{15} + b_{14} \cdot 2^{14} + b_{13} \cdot 2^{13} + b_{12} \cdot 2^{12}) + (b_{11} \cdot 2^{11} + b_{10} \cdot 2^{10} + b_9 \cdot 2^9 + b_8 \cdot 2^8) \\ & + (b_7 \cdot 2^7 + b_6 \cdot 2^6 + b_5 \cdot 2^5 + b_4 \cdot 2^4) + (b_3 \cdot 2^3 + b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0) \end{aligned}$$

Various powers of two can be factored out of the individual groups of 4 terms.

$$\begin{aligned} \text{number} = & (b_{15} \cdot 2^3 + b_{14} \cdot 2^2 + b_{13} \cdot 2^1 + b_{12} \cdot 2^0) \cdot 2^{12} + (b_{11} \cdot 2^3 + b_{10} \cdot 2^2 + b_9 \cdot 2^1 + b_8 \cdot 2^0) \cdot 2^8 \\ & + (b_7 \cdot 2^3 + b_6 \cdot 2^2 + b_5 \cdot 2^1 + b_4 \cdot 2^0) \cdot 2^4 + (b_3 \cdot 2^3 + b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0) \end{aligned}$$

Realizing that  $2^4 = 16$ , the above can be transformed as follows.

$$\begin{aligned} \text{number} = & (b_{15} \cdot 2^3 + b_{14} \cdot 2^2 + b_{13} \cdot 2^1 + b_{12} \cdot 2^0) \cdot 16^3 + (b_{11} \cdot 2^3 + b_{10} \cdot 2^2 + b_9 \cdot 2^1 + b_8 \cdot 2^0) \cdot 16^2 \\ & + (b_7 \cdot 2^3 + b_6 \cdot 2^2 + b_5 \cdot 2^1 + b_4 \cdot 2^0) \cdot 16^1 + (b_3 \cdot 2^3 + b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0) \cdot 16^0 \end{aligned}$$

The traditional decimal number system (base = 10) has the ten symbols (0, 1, 2, 3, 4, 5, 6, 7, 8, 9). The hexadecimal system (base = 16) does not have a corresponding traditional set of 16 symbols. The set (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F) has been adopted.

## Aspects of Computer Architecture

### Number Systems

| Binary | Hexadecimal | Decimal |

|--------|-------------|---------|

| 0000   | 0           | 0       |

| 0001   | 1           | 1       |

| 0010   | 2           | 2       |

| 0011   | 3           | 3       |

| 0100   | 4           | 5       |

| 0101   | 5           | 5       |

| 0110   | 6           | 6       |

| 0111   | 7           | 7       |

| 1000   | 8           | 8       |

| 1001   | 9           | 9       |

| 1010   | A           | 10      |

| 1011   | B           | 11      |

| 1100   | C           | 12      |

| 1101   | D           | 13      |

| 1110   | E           | 14      |

| 1111   | F           | 15      |

| 10000  | 10          | 16      |

The factors of the powers of 16 can be replaced with the symbols  $h_i$

$$\text{number} = h_3 \cdot 16^3 + h_2 \cdot 16^2 + h_1 \cdot 16^1 + h_0 \cdot 16^0$$

$$\text{number} \Rightarrow h_3 h_2 h_1 h_0$$

Thus, the binary number has been converted to the corresponding hexadecimal number with out any excessive arithmetic. Conversion of a hexadecimal number to the corresponding binary number is the inverse process.

## Aspects of Computer Architecture

### Number Systems

As an example the following binary number will be converted to hexadecimal. First, the binary number is grouped into sets of 4 bits.

$$\text{number} = 000100001010101100011100_2$$

$$\text{number} = 0001\ 0000\ 1010\ 1011\ 0001\ 1100_2$$

Then, each set of four bits is replaced with the corresponding hexadecimal symbol. The number can then be regrouped.

$$\text{number} = 1\ 0\ A\ B\ 1\ C_{16}$$

$$\text{number} = 10AB1C_{16}$$

As a second example the following hexadecimal number will be converted to binary.

$$\text{number} = C730_{16}$$

$$\text{number} = C\ 7\ 3\ 0_{16}$$

Each hexadecimal symbol is then replaced with the corresponding set of four binary bits. The number can then be regrouped.

$$\text{number} = 1100\ 0111\ 0011\ 0000_2$$

$$\text{number} = 1100011100110000_2$$

#### 2.2.2. Binary to/from Octal

In this case the terms in the binary representation are grouped into groups of three terms.

$$\begin{aligned} \text{number} = & (0 \cdot 2^{17} + 0 \cdot 2^{16} + b_{15} \cdot 2^{15}) + (b_{14} \cdot 2^{14} + b_{13} \cdot 2^{13} + b_{12} \cdot 2^{12}) \\ & + (b_{11} \cdot 2^{11} + b_{10} \cdot 2^{10} + b_9 \cdot 2^9) + (b_8 \cdot 2^8 + b_7 \cdot 2^7 + b_6 \cdot 2^6) \\ & + (b_5 \cdot 2^5 + b_4 \cdot 2^4 + b_3 \cdot 2^3) + (b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0) \end{aligned}$$

Now factor the appropriate power of two out of each group.

$$\begin{aligned} \text{number} = & (0 \cdot 2^2 + 0 \cdot 2^1 + b_{15} \cdot 2^0) \cdot 2^{15} + (b_{14} \cdot 2^2 + b_{13} \cdot 2^1 + b_{12} \cdot 2^0) \cdot 2^{12} \\ & + (b_{11} \cdot 2^2 + b_{10} \cdot 2^1 + b_9 \cdot 2^0) \cdot 2^9 + (b_8 \cdot 2^2 + b_7 \cdot 2^1 + b_6 \cdot 2^0) \cdot 2^6 \\ & + (b_5 \cdot 2^2 + b_4 \cdot 2^1 + b_3 \cdot 2^0) \cdot 2^3 + (b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0) \cdot 2^0 \end{aligned}$$

Given that  $2^3 = 8$ , the following transformation is made.

## Aspects of Computer Architecture

### Number Systems

$$\begin{aligned} \text{number} = & (0 \cdot 2^2 + 0 \cdot 2^1 + b_{15} \cdot 2^0) \cdot 8^5 + (b_{14} \cdot 2^2 + b_{13} \cdot 2^1 + b_{12} \cdot 2^0) \cdot 8^4 \\ & + (b_{11} \cdot 2^2 + b_{10} \cdot 2^1 + b_9 \cdot 2^0) \cdot 8^3 + (b_8 \cdot 2^2 + b_7 \cdot 2^1 + b_6 \cdot 2^0) \cdot 8^2 \\ & + (b_5 \cdot 2^2 + b_4 \cdot 2^1 + b_3 \cdot 2^0) \cdot 8^1 + (b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0) \cdot 8^0 \end{aligned}$$

The coefficients of the powers of 8 can be replaced by the octal symbols defined below.

| Binary | Octal | Decimal |

|--------|-------|---------|

| 0000   | 0     | 0       |

| 0001   | 1     | 1       |

| 0010   | 2     | 2       |

| 0011   | 3     | 3       |

| 0100   | 4     | 5       |

| 0101   | 5     | 5       |

| 0110   | 6     | 6       |

| 0111   | 7     | 7       |

| 1000   | 10    | 8       |

$$\text{number} = o_5 \cdot 8^5 + o_4 \cdot 8^4 + o_3 \cdot 8^3 + o_2 \cdot 8^2 + o_1 \cdot 8^1 + o_0 \cdot 8^0$$

$$\text{number} \Rightarrow o_4 o_3 o_2 o_1 o_0$$

As an example the following binary number will be converted to octal. First, the binary number is grouped into sets of three bits.

$$\text{number} = 000100001010101100011100_2$$

$$\text{number} = 000 \ 100 \ 001 \ 010 \ 101 \ 100 \ 011 \ 100_2$$

Then each set of three bits is replaced with the corresponding octal symbol. The number can then be regrouped.

## Aspects of Computer Architecture

### Number Systems

number = 0 4 1 2 5 4 3 4<sub>8</sub>

number = 04125434<sub>8</sub>

The inverse operation will serve as a second example. The following octal number will be converted to binary. Begin by separating the octal symbols.

number = 143460<sub>8</sub>

number = 1 4 3 4 6 0<sub>8</sub>

Each octal symbol is then replaced with the corresponding set of three binary bits. The number can then be regrouped.

number = 001 100 011 100 110 000<sub>2</sub>

number = 1100011100110000<sub>2</sub>

## 2.3. Signed Integers

A set of n binary bits,  $b_{n-1}, b_{n-2}, \dots, b_1, b_0$ , may also be used to represent a signed integer. Three different representations have been used.

### 2.3.1. Sign/Magnitude

This representation uses one bit to represent the sign of the number. The most significant bit is used for the sign bit.  $b_s = b_{n-1} = 0$  for a positive number.  $b_s = b_{n-1} = 1$  for a negative number. The absolute value of the number is placed in the remaining bits as an unsigned integer.

Examples, using 16 bit numbers:

## Aspects of Computer Architecture

### Number Systems

| Signed Number | Sign/Magnitude Representation   | Binary | Oct    | Dec   | Hex  |

|---------------|---------------------------------|--------|--------|-------|------|

|               |                                 |        |        |       |      |

| 1             | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 |        | 1      | 1     | 1    |

| -1            | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 |        | 10001  | 32769 | 8001 |

| 32767         | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |        | 77777  | 32767 | 7FFF |

| -32767        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |        | 177777 | 65535 | FFFF |

| 0             | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |        | 000000 | 0     | 0000 |

#### 2.3.2. One's Complement

This representation again uses the most significant bit to represent the sign of the number.  $b_{n-1} = b_s = 0$  for a positive number.  $b_{n-1} = b_s = 1$  for a negative number. The absolute value of the number to be represented has to be less than  $2^{n-1} - 1$ . Convert the absolute value of the number to a binary number of n bits. Since the number is less than  $2^{n-1} - 1$ , the sign bit,  $b_s = b_{n-1}$ , will be zero. If the number being converted is negative, invert all n bits. Notice that the sign bit will be appropriate.

As an example convert the number  $60_{10}$  to one's complement.

0000 0000 0011 1100<sub>2</sub> =  $60_{10}$  = 3C<sub>16</sub> Convert absolute value to binary.

Finished.

Now convert  $-60_{10}$  to one's complement.

0000 0000 0011 1100<sub>2</sub> =  $60_{10}$  = 3C<sub>16</sub> Convert absolute value to binary.

1111 1111 1100 0011<sub>2</sub> =  $65475_{10}$  = FFC3<sub>16</sub> Invert all bits.

Done

Further examples, using 16 bit numbers:

## Aspects of Computer Architecture

### Number Systems

| Signed Number | One's Complement Representation |        |       |      |  |

|---------------|---------------------------------|--------|-------|------|--|

|               | Binary                          | Oct    | Dec   | Hex  |  |

| 1             | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 | 000001 | 1     | 0001 |  |

| -1            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 | 177776 | 65534 | FFFE |  |

| 32767         | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 077777 | 32767 | 7FFF |  |

| -32767        | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 100000 | 32768 | 8000 |  |

| 0             | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 000000 | 0     | 0000 |  |

| -0            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 177777 | 65535 | FFFF |  |

### 2.3.3. Two's Complement

This representation again uses the most significant bit to represent the sign of the number.  $b_s = b_{n-1} = 0$  for a positive number.  $b_s = b_{n-1} = 1$  for a negative number. Again, the absolute value of the number to be represented has to be less than  $2^{n-1} - 1$ . Convert the absolute value of the number to a binary number of n bits. Since the number is less than  $2^{n-1} - 1$ , the sign bit,  $b_s = b_{n-1}$ , will be zero. If the number being converted is negative, invert all n bits. Then add one to the resultant. Notice that the sign bit will be appropriate. This representation avoids the problem of +0 and -0 of the one's complement representation. This is now the typical representation used.

As an example convert the number  $60_{10}$  to two's complement.

$0000\ 0000\ 0011\ 1100_2 = 60_{10} = 3C_{16}$  Convert absolute value to binary.

Finished.

Now convert  $-60_{10}$  to two's complement.

$0000\ 0000\ 0011\ 1100_2 = 60_{10} = 3C_{16}$  Convert absolute value to binary.

$1111\ 1111\ 1100\ 0011_2 = 65475_{10} = FFC3_{16}$  Invert all bits.

$1_2$  Add one.

$1111\ 1111\ 1100\ 0100_2 = 65476_{10} = FFC4_{16}$  Done.

## Aspects of Computer Architecture

### Number Systems

Further examples, using 16 bit numbers:

| Signed Number | Two's Complement                  |         |       |      |   |

|---------------|-----------------------------------|---------|-------|------|---|

|               | Binary                            | Oct     | Dec   | Hex  |   |

| 1             | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1   | 1       | 1     | 1    | 1 |

| -1            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1   | 1777777 | 65535 | FFFF |   |

| 32766         | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0   | 77776   | 32766 | 7FFE |   |

| 32767         | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1   | 77777   | 32767 | 7FFF |   |

| -32766        | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 | 100002  | 32770 | 8002 |   |

| -32767        | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1   | 100001  | 32769 | 8001 |   |

| -32768        | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0   | 100000  | 32768 | 8000 |   |

At this point, a few simple arithmetic examples might be useful. These examples use two's complement arithmetic. First there is the binary addition table for adding two binary single bit numbers (A + B). Multiple bit additions are performed bit by bit with the adding in of any carry from the previous position

| A | B | A+B | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

Add the binary equivalents of  $-60_{10}$  and  $+60_{10}$

|                                    |                                      |

|------------------------------------|--------------------------------------|

| 1 1111 1111 1111 100 <sub>2</sub>  | Carry                                |

| 0000 0000 0011 1100 <sub>2</sub> = | $60_{10} = 3C_{16}$ First number     |

| 1111 1111 1100 0100 <sub>2</sub> = | $-60_{10} = FFC4_{16}$ Second number |

| 0000 0000 0000 0000 <sub>2</sub>   | $0_{10} 0_{16}$ Sum                  |

## Aspects of Computer Architecture

### Number Systems

#### 2.4. Floating Point Numbers

This section summarizes the formats of several of the data types supported by Intel.<sup>1</sup> The value of a floating point number is given by the following

$$\text{number} = (-1)^S (2^{E-\text{Bias}})F$$

where “S” is the sign bit, “E” is the exponent, “F” is the fractional mantissa, and “BIAS” is an integer that varies with representation and is listed below for these particular representations.

<sup>1</sup> “Microprocessors,” page 4-509, Intel Corporation, Literature Sales, PO Box 7641, Mt. Prospect IL 60056-7641, 1990.

# Aspects of Computer Architecture

## Number Systems

Table 1 Number Formats

| Data Type          | Bits | Significant Digits | Range                                                      |

|--------------------|------|--------------------|------------------------------------------------------------|

| Word Integer       | 16   | 4                  | $-32768 \leq X \leq 32767$                                 |

| Short Integer      | 32   | 9                  | $-2 \times 10^9 \leq X \leq 2 \times 10^9$                 |

| Long Integer       | 64   | 18                 | $-9 \times 10^{18} \leq X \leq 9 \times 10^{18}$           |

| Single Precision   | 32   | 6-7                | $8.43 \times 10^{-37} \leq  X  \leq 3.37 \times 10^{38}$   |

| Double Precision   | 64   | 15-16              | $4.19 \times 10^{-307} \leq  X  \leq 1.67 \times 10^{308}$ |

| Extended Precision | 80   | 19                 | $3.4 \times 10^{-4932} \leq  X  \leq 1.2 \times 10^{4932}$ |

Figure 2 Intel Floating Point Storage

# Aspects of Computer Architecture

## Number Systems

Figure 3 Intel Integer Storage

Table 2 Symbol Definitions

| Symbol | Description                                     |

|--------|-------------------------------------------------|

| A      | Base address of the stored number               |

| S      | Sign of the number (0 = positive, 1 = negative) |

| MSB    | Most Significant Bit of integer                 |

| LSB    | Least Significant Bit of Integer                |

| MSF    | Most Significant Bit of fraction                |

| LSF    | Least Significant Bit of fraction               |

| MSE    | Most Significant Bit of the exponent            |

| LSE    | Least Significant Bit of the exponent           |

| Bias   | Single 127 ( $7F_{16}$ )                        |

|        | Double 1023 ( $3FF_{16}$ )                      |

|        | Extended 16383 ( $3FFF_{16}$ )                  |

# Aspects of Computer Architecture

## Number Systems

### 2.5. Useful Tables of Numbers

#### 2.5.1. Powers of Two

Table 3 Powers of 2

| n  | DEC        | OCT         | HEX       | Common Name    |

|----|------------|-------------|-----------|----------------|

| 0  | 1          | 1           | 1         |                |

| 1  | 2          | 2           | 2         |                |

| 2  | 4          | 4           | 4         |                |

| 3  | 8          | 10          | 8         |                |

| 4  | 16         | 20          | 10        |                |

| 5  | 32         | 40          | 20        |                |

| 6  | 64         | 100         | 40        |                |

| 7  | 128        | 200         | 80        |                |

| 8  | 256        | 400         | 100       |                |

| 9  | 512        | 1000        | 200       |                |

| 10 | 1024       | 2000        | 400       | 1K             |

| 11 | 2048       | 4000        | 800       | 2K             |

| 12 | 4096       | 10000       | 1000      | 4K             |

| 13 | 8192       | 20000       | 2000      | 8K             |

| 14 | 16384      | 40000       | 4000      | 16K            |

| 15 | 32768      | 100000      | 8000      | 32K            |

| 16 | 65536      | 200000      | 10000     | 64K            |

| 17 | 131072     | 400000      | 20000     | 128K           |

| 18 | 262144     | 1000000     | 40000     | 256K           |

| 19 | 524288     | 2000000     | 80000     | 512K           |

| 20 | 1048576    | 4000000     | 100000    | 1M or 1Meg     |

| 21 | 2097152    | 1000000     | 200000    | 2M or 2Meg     |

| 22 | 4194304    | 20000000    | 400000    | 4M or 4Meg     |

| 23 | 8388608    | 40000000    | 800000    | 8M or 8Meg     |

| 24 | 16777216   | 100000000   | 1000000   | 16M or 16Meg   |

| 25 | 33554432   | 200000000   | 2000000   | 32M or 32Meg   |

| 26 | 67108864   | 400000000   | 4000000   | 64M or 64Meg   |

| 27 | 134217728  | 1000000000  | 8000000   | 128M or 128Meg |

| 28 | 268435456  | 2000000000  | 10000000  | 256M or 256Meg |

| 29 | 536870912  | 4000000000  | 20000000  | 512M or 512Meg |

| 30 | 1073741824 | 10000000000 | 40000000  | 1G or 1Gig     |

| 31 | 2147483648 | 20000000000 | 80000000  | 2G or 2Gig     |

| 32 | 4294967296 | 40000000000 | 100000000 | 4G or 4Gig     |

## Aspects of Computer Architecture

### Number Systems

The above table contains the values of the first 32 powers of 2 expressed in base 10 (decimal or DEC), base 8 (octal or Oct), and base 16 (hexadecimal or Hex). The right most column of the table contains the common names often given to the corresponding quantities. This nomenclature is an artifact of the computer industry which early on chose to use the short hand name “one K” to represent the much longer and more appropriate name “One thousand twenty four,” etc.

Table 4 Counting in Different Moduli

| DEC | Binary            | OCT | HEX | Items being counted |

|-----|-------------------|-----|-----|---------------------|

| 0   | 0000000000000000  | 0   | 0   |                     |

| 1   | 0000000000000001  | 1   | 1   | *                   |

| 2   | 0000000000000010  | 2   | 2   | **                  |

| 3   | 0000000000000011  | 3   | 3   | ***                 |

| 4   | 00000000000000100 | 4   | 4   | ****                |

| 5   | 00000000000000101 | 5   | 5   | *****               |

| 6   | 00000000000000110 | 6   | 6   | *****               |

| 7   | 00000000000000111 | 7   | 7   | *****               |

| 8   | 00000000000001000 | 10  | 8   | *****               |

| 9   | 00000000000001001 | 11  | 9   | *****               |

| 10  | 00000000000001010 | 12  | A   | *****               |

| 11  | 00000000000001011 | 13  | B   | *****               |

| 12  | 00000000000001100 | 14  | C   | *****               |

| 13  | 00000000000001101 | 15  | D   | *****               |

| 14  | 00000000000001110 | 16  | E   | *****               |

| 15  | 00000000000001111 | 17  | F   | *****               |

| 16  | 00000000000010000 | 20  | 10  | *****               |

| 17  | 00000000000010001 | 21  | 11  | *****               |

| 18  | 00000000000010010 | 22  | 12  | *****               |

| 19  | 00000000000010011 | 23  | 13  | *****               |

| 20  | 00000000000010100 | 24  | 14  | *****               |

| 21  | 00000000000010101 | 25  | 15  | *****               |

| 22  | 00000000000010110 | 26  | 16  | *****               |

| 23  | 00000000000010111 | 27  | 17  | *****               |

| 24  | 00000000000011000 | 30  | 18  | *****               |

| 25  | 00000000000011001 | 31  | 19  | *****               |

| 26  | 00000000000011010 | 32  | 1A  | *****               |

| 27  | 00000000000011011 | 33  | 1B  | *****               |

| 28  | 00000000000011100 | 34  | 1C  | *****               |

| 29  | 00000000000011101 | 35  | 1D  | *****               |

| 30  | 00000000000011110 | 36  | 1E  | *****               |

| 31  | 00000000000011111 | 37  | 1F  | *****               |

| 32  | 00000000000100000 | 40  | 20  | *****               |

| 33  | 00000000000100001 | 41  | 21  | *****               |

# Aspects of Computer Architecture

## Number Systems

Table 5 0 to 65536 in Multiple Moduli

| DEC | BIN                | BIN                   | OCT | BIN                 | HEX | DEC |

|-----|--------------------|-----------------------|-----|---------------------|-----|-----|

| 0   | 0000000000000000   | 0 000 000 000 000 000 | 0   | 0000 0000 0000 0000 | 0   | 0   |

| 1   | 0000000000000001   | 0 000 000 000 000 001 | 1   | 0000 0000 0000 0001 | 1   | 1   |

| 2   | 0000000000000010   | 0 000 000 000 000 010 | 2   | 0000 0000 0000 0010 | 2   | 2   |

| 3   | 0000000000000011   | 0 000 000 000 000 011 | 3   | 0000 0000 0000 0011 | 3   | 3   |

| 4   | 0000000000000100   | 0 000 000 000 000 100 | 4   | 0000 0000 0000 0100 | 4   | 4   |

| 5   | 0000000000000101   | 0 000 000 000 000 101 | 5   | 0000 0000 0000 0101 | 5   | 5   |

| 6   | 0000000000000110   | 0 000 000 000 000 110 | 6   | 0000 0000 0000 0110 | 6   | 6   |

| 7   | 0000000000000111   | 0 000 000 000 000 111 | 7   | 0000 0000 0000 0111 | 7   | 7   |

| 8   | 0000000000001000   | 0 000 000 000 001 000 | 10  | 0000 0000 0000 1000 | 8   | 8   |

| 9   | 0000000000001001   | 0 000 000 000 001 001 | 11  | 0000 0000 0000 1001 | 9   | 9   |

| 10  | 0000000000001010   | 0 000 000 000 001 010 | 12  | 0000 0000 0000 1010 | A   | 10  |

| 11  | 0000000000001011   | 0 000 000 000 001 011 | 13  | 0000 0000 0000 1011 | B   | 11  |

| 12  | 0000000000001100   | 0 000 000 000 001 100 | 14  | 0000 0000 0000 1100 | C   | 12  |

| 13  | 0000000000001101   | 0 000 000 000 001 101 | 15  | 0000 0000 0000 1101 | D   | 13  |

| 14  | 0000000000001110   | 0 000 000 000 001 110 | 16  | 0000 0000 0000 1110 | E   | 14  |

| 15  | 0000000000001111   | 0 000 000 000 001 111 | 17  | 0000 0000 0000 1111 | F   | 15  |

| 16  | 00000000000010000  | 0 000 000 000 010 000 | 20  | 0000 0000 0001 0000 | 10  | 16  |

| 17  | 00000000000010001  | 0 000 000 000 010 001 | 21  | 0000 0000 0001 0001 | 11  | 17  |

| 18  | 00000000000010010  | 0 000 000 000 010 010 | 22  | 0000 0000 0001 0010 | 12  | 18  |

| 19  | 00000000000010011  | 0 000 000 000 010 011 | 23  | 0000 0000 0001 0011 | 13  | 19  |

| 20  | 00000000000010100  | 0 000 000 000 010 100 | 24  | 0000 0000 0001 0100 | 14  | 20  |

| 21  | 00000000000010101  | 0 000 000 000 010 101 | 25  | 0000 0000 0001 0101 | 15  | 21  |

| 22  | 00000000000010110  | 0 000 000 000 010 110 | 26  | 0000 0000 0001 0110 | 16  | 22  |

| 23  | 00000000000010111  | 0 000 000 000 010 111 | 27  | 0000 0000 0001 0111 | 17  | 23  |

| 24  | 00000000000011000  | 0 000 000 000 011 000 | 30  | 0000 0000 0001 1000 | 18  | 24  |

| 25  | 00000000000011001  | 0 000 000 000 011 001 | 31  | 0000 0000 0001 1001 | 19  | 25  |

| 26  | 00000000000011010  | 0 000 000 000 011 010 | 32  | 0000 0000 0001 1010 | 1A  | 26  |

| 27  | 00000000000011011  | 0 000 000 000 011 011 | 33  | 0000 0000 0001 1011 | 1B  | 27  |

| 28  | 00000000000011100  | 0 000 000 000 011 100 | 34  | 0000 0000 0001 1100 | 1C  | 28  |

| 29  | 00000000000011101  | 0 000 000 000 011 101 | 35  | 0000 0000 0001 1101 | 1D  | 29  |

| 30  | 00000000000011110  | 0 000 000 000 011 110 | 36  | 0000 0000 0001 1110 | 1E  | 30  |

| 31  | 00000000000011111  | 0 000 000 000 011 111 | 37  | 0000 0000 0001 1111 | 1F  | 31  |

| 32  | 000000000000100000 | 0 000 000 000 100 000 | 40  | 0000 0000 0010 0000 | 20  | 32  |

| 33  | 000000000000100001 | 0 000 000 000 100 001 | 41  | 0000 0000 0010 0001 | 21  | 33  |

| 34  | 000000000000100010 | 0 000 000 000 100 010 | 42  | 0000 0000 0010 0010 | 22  | 34  |

| 35  | 000000000000100011 | 0 000 000 000 100 011 | 43  | 0000 0000 0010 0011 | 23  | 35  |

| 36  | 000000000000100100 | 0 000 000 000 100 100 | 44  | 0000 0000 0010 0100 | 24  | 36  |

| 37  | 000000000000100101 | 0 000 000 000 100 101 | 45  | 0000 0000 0010 0101 | 25  | 37  |

| 38  | 000000000000100110 | 0 000 000 000 100 110 | 46  | 0000 0000 0010 0110 | 26  | 38  |

| 39  | 000000000000100111 | 0 000 000 000 100 111 | 47  | 0000 0000 0010 0111 | 27  | 39  |

| 40  | 000000000000101000 | 0 000 000 000 101 000 | 50  | 0000 0000 0010 1000 | 28  | 40  |

# Aspects of Computer Architecture

## Number Systems

| DEC | BIN              | BIN                   | OCT | BIN                 | HEX | DEC |

|-----|------------------|-----------------------|-----|---------------------|-----|-----|

| 41  | 0000000000101001 | 0 000 000 000 101 001 | 51  | 0000 0000 0010 1001 | 29  | 41  |

| 42  | 0000000000101010 | 0 000 000 000 101 010 | 52  | 0000 0000 0010 1010 | 2A  | 42  |

| 43  | 0000000000101011 | 0 000 000 000 101 011 | 53  | 0000 0000 0010 1011 | 2B  | 43  |

| 44  | 0000000000101100 | 0 000 000 000 101 100 | 54  | 0000 0000 0010 1100 | 2C  | 44  |

| 45  | 0000000000101101 | 0 000 000 000 101 101 | 55  | 0000 0000 0010 1101 | 2D  | 45  |

| 46  | 0000000000101110 | 0 000 000 000 101 110 | 56  | 0000 0000 0010 1110 | 2E  | 46  |

| 47  | 0000000000101111 | 0 000 000 000 101 111 | 57  | 0000 0000 0010 1111 | 2F  | 47  |

| 48  | 0000000000110000 | 0 000 000 000 110 000 | 60  | 0000 0000 0011 0000 | 30  | 48  |

| 49  | 0000000000110001 | 0 000 000 000 110 001 | 61  | 0000 0000 0011 0001 | 31  | 49  |

| 50  | 0000000000110010 | 0 000 000 000 110 010 | 62  | 0000 0000 0011 0010 | 32  | 50  |

| 51  | 0000000000110011 | 0 000 000 000 110 011 | 63  | 0000 0000 0011 0011 | 33  | 51  |

| 52  | 0000000000110100 | 0 000 000 000 110 100 | 64  | 0000 0000 0011 0100 | 34  | 52  |

| 53  | 0000000000110101 | 0 000 000 000 110 101 | 65  | 0000 0000 0011 0101 | 35  | 53  |

| 54  | 0000000000110110 | 0 000 000 000 110 110 | 66  | 0000 0000 0011 0110 | 36  | 54  |

| 55  | 0000000000110111 | 0 000 000 000 110 111 | 67  | 0000 0000 0011 0111 | 37  | 55  |

| 56  | 0000000000111000 | 0 000 000 000 111 000 | 70  | 0000 0000 0011 1000 | 38  | 56  |

| 57  | 0000000000111001 | 0 000 000 000 111 001 | 71  | 0000 0000 0011 1001 | 39  | 57  |

| 58  | 0000000000111010 | 0 000 000 000 111 010 | 72  | 0000 0000 0011 1010 | 3A  | 58  |

| 59  | 0000000000111011 | 0 000 000 000 111 011 | 73  | 0000 0000 0011 1011 | 3B  | 59  |

| 60  | 0000000000111100 | 0 000 000 000 111 100 | 74  | 0000 0000 0011 1100 | 3C  | 60  |

| 61  | 0000000000111101 | 0 000 000 000 111 101 | 75  | 0000 0000 0011 1101 | 3D  | 61  |

| 62  | 0000000000111110 | 0 000 000 000 111 110 | 76  | 0000 0000 0011 1110 | 3E  | 62  |

| 63  | 0000000000111111 | 0 000 000 000 111 111 | 77  | 0000 0000 0011 1111 | 3F  | 63  |

| 64  | 000000001000000  | 0 000 000 001 000 000 | 100 | 0000 0000 0100 0000 | 40  | 64  |

| 65  | 000000001000001  | 0 000 000 001 000 001 | 101 | 0000 0000 0100 0001 | 41  | 65  |

| 66  | 000000001000010  | 0 000 000 001 000 010 | 102 | 0000 0000 0100 0010 | 42  | 66  |

| 67  | 000000001000011  | 0 000 000 001 000 011 | 103 | 0000 0000 0100 0011 | 43  | 67  |

| 68  | 000000001000100  | 0 000 000 001 000 100 | 104 | 0000 0000 0100 0100 | 44  | 68  |

| 69  | 000000001000101  | 0 000 000 001 000 101 | 105 | 0000 0000 0100 0101 | 45  | 69  |

| 70  | 000000001000110  | 0 000 000 001 000 110 | 106 | 0000 0000 0100 0110 | 46  | 70  |

| 71  | 000000001000111  | 0 000 000 001 000 111 | 107 | 0000 0000 0100 0111 | 47  | 71  |

| 72  | 000000001001000  | 0 000 000 001 001 000 | 110 | 0000 0000 0100 1000 | 48  | 72  |

| 73  | 000000001001001  | 0 000 000 001 001 001 | 111 | 0000 0000 0100 1001 | 49  | 73  |

| 74  | 000000001001010  | 0 000 000 001 001 010 | 112 | 0000 0000 0100 1010 | 4A  | 74  |

| 75  | 000000001001011  | 0 000 000 001 001 011 | 113 | 0000 0000 0100 1011 | 4B  | 75  |

| 76  | 000000001001100  | 0 000 000 001 001 100 | 114 | 0000 0000 0100 1100 | 4C  | 76  |

| 77  | 000000001001101  | 0 000 000 001 001 101 | 115 | 0000 0000 0100 1101 | 4D  | 77  |

| 78  | 000000001001110  | 0 000 000 001 001 110 | 116 | 0000 0000 0100 1110 | 4E  | 78  |

| 79  | 000000001001111  | 0 000 000 001 001 111 | 117 | 0000 0000 0100 1111 | 4F  | 79  |

| 80  | 0000000001010000 | 0 000 000 001 010 000 | 120 | 0000 0000 0101 0000 | 50  | 80  |

# Aspects of Computer Architecture

## Number Systems

| DEC | BIN              | BIN                   | OCT | BIN                 | HEX | DEC |

|-----|------------------|-----------------------|-----|---------------------|-----|-----|

| 81  | 0000000001010001 | 0 000 000 001 010 001 | 121 | 0000 0000 0101 0001 | 51  | 81  |

| 82  | 0000000001010010 | 0 000 000 001 010 010 | 122 | 0000 0000 0101 0010 | 52  | 82  |

| 83  | 0000000001010011 | 0 000 000 001 010 011 | 123 | 0000 0000 0101 0011 | 53  | 83  |

| 84  | 0000000001010100 | 0 000 000 001 010 100 | 124 | 0000 0000 0101 0100 | 54  | 84  |

| 85  | 0000000001010101 | 0 000 000 001 010 101 | 125 | 0000 0000 0101 0101 | 55  | 85  |

| 86  | 0000000001010110 | 0 000 000 001 010 110 | 126 | 0000 0000 0101 0110 | 56  | 86  |

| 87  | 0000000001010111 | 0 000 000 001 010 111 | 127 | 0000 0000 0101 0111 | 57  | 87  |

| 88  | 0000000001011000 | 0 000 000 001 011 000 | 130 | 0000 0000 0101 1000 | 58  | 88  |

| 89  | 0000000001011001 | 0 000 000 001 011 001 | 131 | 0000 0000 0101 1001 | 59  | 89  |

| 90  | 0000000001011010 | 0 000 000 001 011 010 | 132 | 0000 0000 0101 1010 | 5A  | 90  |

| 91  | 0000000001011011 | 0 000 000 001 011 011 | 133 | 0000 0000 0101 1011 | 5B  | 91  |

| 92  | 0000000001011100 | 0 000 000 001 011 100 | 134 | 0000 0000 0101 1100 | 5C  | 92  |

| 93  | 0000000001011101 | 0 000 000 001 011 101 | 135 | 0000 0000 0101 1101 | 5D  | 93  |

| 94  | 0000000001011110 | 0 000 000 001 011 110 | 136 | 0000 0000 0101 1110 | 5E  | 94  |

| 95  | 0000000001011111 | 0 000 000 001 011 111 | 137 | 0000 0000 0101 1111 | 5F  | 95  |

| 96  | 0000000001100000 | 0 000 000 001 100 000 | 140 | 0000 0000 0110 0000 | 60  | 96  |

| 97  | 0000000001100001 | 0 000 000 001 100 001 | 141 | 0000 0000 0110 0001 | 61  | 97  |

| 98  | 0000000001100010 | 0 000 000 001 100 010 | 142 | 0000 0000 0110 0010 | 62  | 98  |

| 99  | 0000000001100011 | 0 000 000 001 100 011 | 143 | 0000 0000 0110 0011 | 63  | 99  |

| 100 | 0000000001100100 | 0 000 000 001 100 100 | 144 | 0000 0000 0110 0100 | 64  | 100 |

| 101 | 0000000001100101 | 0 000 000 001 100 101 | 145 | 0000 0000 0110 0101 | 65  | 101 |

| 102 | 0000000001100110 | 0 000 000 001 100 110 | 146 | 0000 0000 0110 0110 | 66  | 102 |

| 103 | 0000000001100111 | 0 000 000 001 100 111 | 147 | 0000 0000 0110 0111 | 67  | 103 |

| 104 | 0000000001101000 | 0 000 000 001 101 000 | 150 | 0000 0000 0110 1000 | 68  | 104 |

| 105 | 0000000001101001 | 0 000 000 001 101 001 | 151 | 0000 0000 0110 1001 | 69  | 105 |

| 106 | 0000000001101010 | 0 000 000 001 101 010 | 152 | 0000 0000 0110 1010 | 6A  | 106 |

| 107 | 0000000001101011 | 0 000 000 001 101 011 | 153 | 0000 0000 0110 1011 | 6B  | 107 |

| 108 | 0000000001101100 | 0 000 000 001 101 100 | 154 | 0000 0000 0110 1100 | 6C  | 108 |

| 109 | 0000000001101101 | 0 000 000 001 101 101 | 155 | 0000 0000 0110 1101 | 6D  | 109 |

| 110 | 0000000001101110 | 0 000 000 001 101 110 | 156 | 0000 0000 0110 1110 | 6E  | 110 |

| 111 | 0000000001101111 | 0 000 000 001 101 111 | 157 | 0000 0000 0110 1111 | 6F  | 111 |

| 112 | 0000000001110000 | 0 000 000 001 110 000 | 160 | 0000 0000 0111 0000 | 70  | 112 |

| 113 | 0000000001110001 | 0 000 000 001 110 001 | 161 | 0000 0000 0111 0001 | 71  | 113 |

| 114 | 0000000001110010 | 0 000 000 001 110 010 | 162 | 0000 0000 0111 0010 | 72  | 114 |

| 115 | 0000000001110011 | 0 000 000 001 110 011 | 163 | 0000 0000 0111 0011 | 73  | 115 |

| 116 | 0000000001110100 | 0 000 000 001 110 100 | 164 | 0000 0000 0111 0100 | 74  | 116 |

| 117 | 0000000001110101 | 0 000 000 001 110 101 | 165 | 0000 0000 0111 0101 | 75  | 117 |

| 118 | 0000000001110110 | 0 000 000 001 110 110 | 166 | 0000 0000 0111 0110 | 76  | 118 |

| 119 | 0000000001110111 | 0 000 000 001 110 111 | 167 | 0000 0000 0111 0111 | 77  | 119 |

| 120 | 0000000001111000 | 0 000 000 001 111 000 | 170 | 0000 0000 0111 1000 | 78  | 120 |

# Aspects of Computer Architecture

## Number Systems

| DEC   | BIN               | BIN                   | OCT    | BIN                 | HEX  | DEC   |

|-------|-------------------|-----------------------|--------|---------------------|------|-------|

| 121   | 0000000001111001  | 0 000 000 001 111 001 | 171    | 0000 0000 0111 1001 | 79   | 121   |

| 122   | 0000000001111010  | 0 000 000 001 111 010 | 172    | 0000 0000 0111 1010 | 7A   | 122   |

| 123   | 0000000001111011  | 0 000 000 001 111 011 | 173    | 0000 0000 0111 1011 | 7B   | 123   |

| 124   | 0000000001111100  | 0 000 000 001 111 100 | 174    | 0000 0000 0111 1100 | 7C   | 124   |

| 125   | 0000000001111101  | 0 000 000 001 111 101 | 175    | 0000 0000 0111 1101 | 7D   | 125   |

| 126   | 0000000001111110  | 0 000 000 001 111 110 | 176    | 0000 0000 0111 1110 | 7E   | 126   |

| 127   | 0000000001111111  | 0 000 000 001 111 111 | 177    | 0000 0000 0111 1111 | 7F   | 127   |

| 128   | 0000000010000000  | 0 000 000 010 000 000 | 200    | 0000 0000 1000 0000 | 80   | 128   |

| 129   | 0000000010000001  | 0 000 000 010 000 001 | 201    | 0000 0000 1000 0001 | 81   | 129   |

| 130   | 0000000010000010  | 0 000 000 010 000 010 | 202    | 0000 0000 1000 0010 | 82   | 130   |

| 65530 | 1111111111111010  | 1 111 111 111 111 010 | 177772 | 1111 1111 1111 1010 | FFFA | 65530 |

| 65531 | 1111111111111011  | 1 111 111 111 111 011 | 177773 | 1111 1111 1111 1011 | FFFB | 65531 |

| 65532 | 1111111111111100  | 1 111 111 111 111 100 | 177774 | 1111 1111 1111 1100 | FFFC | 65532 |

| 65533 | 1111111111111101  | 1 111 111 111 111 101 | 177775 | 1111 1111 1111 1101 | FFFD | 65533 |

| 65534 | 1111111111111110  | 1 111 111 111 111 110 | 177776 | 1111 1111 1111 1110 | FFFE | 65534 |

| 65535 | 1111111111111111  | 1 111 111 111 111 111 | 177777 | 1111 1111 1111 1111 | FFFF | 65535 |

| 65536 | 0000000000000000  | 0 000 000 000 000 000 | 0      | 0000 0000 0000 0000 | 0    | 65536 |

| 65537 | 0000000000000001  | 0 000 000 000 000 001 | 1      | 0000 0000 0000 0001 | 1    | 65537 |

| 65538 | 0000000000000010  | 0 000 000 000 000 010 | 2      | 0000 0000 0000 0010 | 2    | 65538 |

| 65539 | 0000000000000011  | 0 000 000 000 000 011 | 3      | 0000 0000 0000 0011 | 3    | 65539 |

| 65540 | 00000000000000100 | 0 000 000 000 000 100 | 4      | 0000 0000 0000 0100 | 4    | 65540 |

# Aspects of Computer Architecture

## Character Codes

### 3. Character Codes

#### 3.1. Six Bit Character Codes

These codes were used in the early days of computing when memory and bandwidth was very expensive. Notice that there are only upper case characters.

Table 6 Six Bit Character Codes

| Char | Octal | Dec | Hex | Char  | Octal | Dec | Hex |

|------|-------|-----|-----|-------|-------|-----|-----|

| @    | 0     | 0   | 0   | space | 40    | 32  | 20  |

| A    | 1     | 1   | 1   | !     | 41    | 33  | 21  |

| B    | 2     | 2   | 2   | "     | 42    | 34  | 22  |

| C    | 3     | 3   | 3   | #     | 43    | 35  | 23  |

| D    | 4     | 4   | 4   | \$    | 44    | 36  | 24  |

| E    | 5     | 5   | 5   | %     | 45    | 37  | 25  |

| F    | 6     | 6   | 6   | &     | 46    | 38  | 26  |

| G    | 7     | 7   | 7   | '     | 47    | 39  | 27  |

| H    | 10    | 8   | 8   | (     | 50    | 40  | 28  |

| I    | 11    | 9   | 9   | )     | 51    | 41  | 29  |

| J    | 12    | 10  | A   | *     | 52    | 42  | 2A  |

| K    | 13    | 11  | B   | +     | 53    | 43  | 2B  |

| L    | 14    | 12  | C   | ,     | 54    | 44  | 2C  |

| M    | 15    | 13  | D   | -     | 55    | 45  | 2D  |

| N    | 16    | 14  | E   | .     | 56    | 46  | 2E  |

| O    | 17    | 15  | F   | /     | 57    | 47  | 2F  |

| P    | 20    | 16  | 10  | 0     | 60    | 48  | 30  |

| Q    | 21    | 17  | 11  | 1     | 61    | 49  | 31  |

| R    | 22    | 18  | 12  | 2     | 62    | 50  | 32  |

| S    | 23    | 19  | 13  | 3     | 63    | 51  | 33  |

| T    | 24    | 20  | 14  | 4     | 64    | 52  | 34  |

| U    | 25    | 21  | 15  | 5     | 65    | 53  | 35  |

| V    | 26    | 22  | 16  | 6     | 66    | 54  | 36  |

| W    | 27    | 23  | 17  | 7     | 67    | 55  | 37  |

| X    | 30    | 24  | 18  | 8     | 70    | 56  | 38  |

| Y    | 31    | 25  | 19  | 9     | 71    | 57  | 39  |

| Z    | 32    | 26  | 1A  | :     | 72    | 58  | 3A  |

| [    | 33    | 27  | 1B  | ;     | 73    | 59  | 3B  |

| \    | 34    | 28  | 1C  | <     | 74    | 60  | 3C  |

| ]    | 35    | 29  | 1D  | =     | 75    | 61  | 3D  |

| ^    | 36    | 30  | 1E  | >     | 76    | 62  | 3E  |

|      | 37    | 31  | 1F  | ?     | 77    | 63  | 3F  |

# Aspects of Computer Architecture

## Character Codes

### 3.2. ASCII Character Codes

Table 7 ASCII Character Codes

| Character | Octal | Dec | Hex | Char | Octal | Dec | Hex | Char | Octal | Dec | Hex | Char | Octal | Dec | Hex |

|-----------|-------|-----|-----|------|-------|-----|-----|------|-------|-----|-----|------|-------|-----|-----|

| <NULL>    | 0     | 0   | 0   |      | 40    | 32  | 20  | @    | 100   | 64  | 40  | `    | 140   | 96  | 60  |

| <SOH>     | 1     | 1   | 1   | !    | 41    | 33  | 21  | A    | 101   | 65  | 41  | a    | 141   | 97  | 61  |

| <STX>     | 2     | 2   | 2   | "    | 42    | 34  | 22  | B    | 102   | 66  | 42  | b    | 142   | 98  | 62  |

| <ETX>     | 3     | 3   | 3   | #    | 43    | 35  | 23  | C    | 103   | 67  | 43  | c    | 143   | 99  | 63  |

| <EOT>     | 4     | 4   | 4   | \$   | 44    | 36  | 24  | D    | 104   | 68  | 44  | d    | 144   | 100 | 64  |

| <ENQ>     | 5     | 5   | 5   | %    | 45    | 37  | 25  | E    | 105   | 69  | 45  | e    | 145   | 101 | 65  |

| <ACK>     | 6     | 6   | 6   | &    | 46    | 38  | 26  | F    | 106   | 70  | 46  | f    | 146   | 102 | 66  |

| <BEL>     | 7     | 7   | 7   | '    | 47    | 39  | 27  | G    | 107   | 71  | 47  | g    | 147   | 103 | 67  |

| <BS>      | 10    | 8   | 8   | (    | 50    | 40  | 28  | H    | 110   | 72  | 48  | h    | 150   | 104 | 68  |

| <HT>      | 11    | 9   | 9   | )    | 51    | 41  | 29  | I    | 111   | 73  | 49  | i    | 151   | 105 | 69  |

| <LF>      | 12    | 10  | A   | *    | 52    | 42  | 2A  | J    | 112   | 74  | 4A  | j    | 152   | 106 | 6A  |

| <VT>      | 13    | 11  | B   | +    | 53    | 43  | 2B  | K    | 113   | 75  | 4B  | k    | 153   | 107 | 6B  |

| <FF>      | 14    | 12  | C   | ,    | 54    | 44  | 2C  | L    | 114   | 76  | 4C  | l    | 154   | 108 | 6C  |

| <CR>      | 15    | 13  | D   | -    | 55    | 45  | 2D  | M    | 115   | 77  | 4D  | m    | 155   | 109 | 6D  |

| <SO>      | 16    | 14  | E   | .    | 56    | 46  | 2E  | N    | 116   | 78  | 4E  | n    | 156   | 110 | 6E  |

| <SI>      | 17    | 15  | F   | /    | 57    | 47  | 2F  | O    | 117   | 79  | 4F  | o    | 157   | 111 | 6F  |

| <DLE>     | 20    | 16  | 10  | 0    | 60    | 48  | 30  | P    | 120   | 80  | 50  | p    | 160   | 112 | 70  |

| <DC1>     | 21    | 17  | 11  | 1    | 61    | 49  | 31  | Q    | 121   | 81  | 51  | q    | 161   | 113 | 71  |

| <DC2>     | 22    | 18  | 12  | 2    | 62    | 50  | 32  | R    | 122   | 82  | 52  | r    | 162   | 114 | 72  |

| <DC3>     | 23    | 19  | 13  | 3    | 63    | 51  | 33  | S    | 123   | 83  | 53  | s    | 163   | 115 | 73  |

| <DC4>     | 24    | 20  | 14  | 4    | 64    | 52  | 34  | T    | 124   | 84  | 54  | t    | 164   | 116 | 74  |

| <NAK>     | 25    | 21  | 15  | 5    | 65    | 53  | 35  | U    | 125   | 85  | 55  | u    | 165   | 117 | 75  |

| <SYN>     | 26    | 22  | 16  | 6    | 66    | 54  | 36  | V    | 126   | 86  | 56  | v    | 166   | 118 | 76  |

| <ETB>     | 27    | 23  | 17  | 7    | 67    | 55  | 37  | W    | 127   | 87  | 57  | w    | 167   | 119 | 77  |

| <CAN>     | 30    | 24  | 18  | 8    | 70    | 56  | 38  | X    | 130   | 88  | 58  | x    | 170   | 120 | 78  |

| <EM>      | 31    | 25  | 19  | 9    | 71    | 57  | 39  | Y    | 131   | 89  | 59  | y    | 171   | 121 | 79  |

| <SUB>     | 32    | 26  | 1A  | :    | 72    | 58  | 3A  | Z    | 132   | 90  | 5A  | z    | 172   | 122 | 7A  |

| <ESC>     | 33    | 27  | 1B  | ;    | 73    | 59  | 3B  | [    | 133   | 91  | 5B  | {    | 173   | 123 | 7B  |

| <FS>      | 34    | 28  | 1C  | <    | 74    | 60  | 3C  | \    | 134   | 92  | 5C  |      | 174   | 124 | 7C  |

| <GS>      | 35    | 29  | 1D  | =    | 75    | 61  | 3D  | ]    | 135   | 93  | 5D  | }    | 175   | 125 | 7D  |

| <RS>      | 36    | 30  | 1E  | >    | 76    | 62  | 3E  | ^    | 136   | 94  | 5E  | ~    | 176   | 126 | 7E  |

| <US>      | 37    | 31  | 1F  | ?    | 77    | 63  | 3F  | -    | 137   | 95  | 5F  | DEL  | 177   | 127 | 7F  |

## Aspects of Computer Architecture

### Character Codes

Table 8 ASCII Control Characters

|       |                                         |

|-------|-----------------------------------------|

| <NUL> | Null                                    |

| <SOH> | Start of heading                        |

| <STX> | Start of text                           |

| <ETX> | End of text                             |

| <EOT> | End of transmission                     |

| <ENQ> | Enquiry                                 |

| <ACK> | Acknowledge                             |

| <BEL> | Bell (audible signal)                   |

| <BS>  | Backspace                               |

| <HT>  | Horizontal Tabulation                   |

| <LF>  | Line Feed - go to new line              |

| <VT>  | Vertical tabulation                     |

| <FF>  | Form Feed - go to new page              |

| <CR>  | Carriage return - return to left margin |

| <SO>  | Shift out                               |

| <SI>  | Shift in                                |

| <DLE> | Data link escape                        |

| <DC1> | Device Control 1 - XON                  |

| <DC2> | Device Control 2                        |

| <DC3> | Device Control 3 - XOFF                 |

| <DC4> | Device Control 4                        |

| <NAK> | Negative Acknowledge                    |

| <SYN> | Synchronous idle                        |

| <ETB> | End of transmission block               |

| <CAN> | Cancel                                  |

| <EM>  | End of medium                           |

| <SUB> | Substitute                              |

| <ESC> | Escape                                  |

| <FS>  | File Separator                          |

| <GS>  | Group Separator                         |

| <RS>  | Record Separator                        |

| <US>  | Unit Separator                          |

| <DEL> | Delete                                  |

# Aspects of Computer Architecture

## Character Codes

### 3.3. ANSI Character Codes

Table 9 ANSI Character Set

The ANSI character set consists of the ASCII character set plus the set of characters in this table.

| Char | Octal | Dec | Hex |

|------|-------|-----|-----|------|-------|-----|-----|------|-------|-----|-----|------|-------|-----|-----|

|      | 200   | 128 | 80  |      | 240   | 160 | A0  | À    | 300   | 192 | C0  | à    | 340   | 224 | E0  |

|      | 201   | 129 | 81  | í    | 241   | 161 | A1  | Á    | 301   | 193 | C1  | á    | 341   | 225 | E1  |

| ,    | 202   | 130 | 82  | ¢    | 242   | 162 | A2  | Â    | 302   | 194 | C2  | â    | 342   | 226 | E2  |

| f    | 203   | 131 | 83  | £    | 243   | 163 | A3  | Ã    | 303   | 195 | C3  | ã    | 343   | 227 | E3  |

| „    | 204   | 132 | 84  | ¤    | 244   | 164 | A4  | Ä    | 304   | 196 | C4  | ä    | 344   | 228 | E4  |

| ...  | 205   | 133 | 85  | ¥    | 245   | 165 | A5  | Å    | 305   | 197 | C5  | å    | 345   | 229 | E5  |

| †    | 206   | 134 | 86  | ¡    | 246   | 166 | A6  | Æ    | 306   | 198 | C6  | æ    | 346   | 230 | E6  |

| ‡    | 207   | 135 | 87  | §    | 247   | 167 | A7  | Ç    | 307   | 199 | C7  | ç    | 347   | 231 | E7  |

| ^    | 210   | 136 | 88  | „    | 250   | 168 | A8  | È    | 310   | 200 | C8  | è    | 350   | 232 | E8  |

| %o   | 211   | 137 | 89  | ©    | 251   | 169 | A9  | É    | 311   | 201 | C9  | é    | 351   | 233 | E9  |

| Š    | 212   | 138 | 8A  | ª    | 252   | 170 | AA  | Ê    | 312   | 202 | CA  | ê    | 352   | 234 | EA  |

| „    | 213   | 139 | 8B  | «    | 253   | 171 | AB  | Ë    | 313   | 203 | CB  | ë    | 353   | 235 | EB  |

| Œ    | 214   | 140 | 8C  | ¬    | 254   | 172 | AC  | Ì    | 314   | 204 | CC  | ì    | 354   | 236 | EC  |

|      | 215   | 141 | 8D  | -    | 255   | 173 | AD  | Í    | 315   | 205 | CD  | í    | 355   | 237 | ED  |

|      | 216   | 142 | 8E  | ®    | 256   | 174 | AE  | Î    | 316   | 206 | CE  | î    | 356   | 238 | EE  |

|      | 217   | 143 | 8F  | -    | 257   | 175 | AF  | Ï    | 317   | 207 | CF  | ï    | 357   | 239 | EF  |

|      | 220   | 144 | 90  | °    | 260   | 176 | B0  | Ð    | 320   | 208 | D0  | ð    | 360   | 240 | F0  |

| ‘    | 221   | 145 | 91  | ±    | 261   | 177 | B1  | Ñ    | 321   | 209 | D1  | ñ    | 361   | 241 | F1  |

| ’    | 222   | 146 | 92  | ²    | 262   | 178 | B2  | Ò    | 322   | 210 | D2  | ò    | 362   | 242 | F2  |

| “    | 223   | 147 | 93  | ³    | 263   | 179 | B3  | Ó    | 323   | 211 | D3  | ó    | 363   | 243 | F3  |

| ”    | 224   | 148 | 94  | ’    | 264   | 180 | B4  | Ô    | 324   | 212 | D4  | ô    | 364   | 244 | F4  |

| •    | 225   | 149 | 95  | µ    | 265   | 181 | B5  | Õ    | 325   | 213 | D5  | õ    | 365   | 245 | F5  |

| -    | 226   | 150 | 96  | ¶    | 266   | 182 | B6  | Ö    | 326   | 214 | D6  | ö    | 366   | 246 | F6  |

| —    | 227   | 151 | 97  | ·    | 267   | 183 | B7  | ×    | 327   | 215 | D7  | ÷    | 367   | 247 | F7  |

| ~    | 230   | 152 | 98  | ,    | 270   | 184 | B8  | Ø    | 330   | 216 | D8  | ø    | 370   | 248 | F8  |

| TM   | 231   | 153 | 99  | ¹    | 271   | 185 | B9  | Ù    | 331   | 217 | D9  | ù    | 371   | 249 | F9  |

| š    | 232   | 154 | 9A  | º    | 272   | 186 | BA  | Ú    | 332   | 218 | DA  | ú    | 372   | 250 | FA  |

| >    | 233   | 155 | 9B  | »    | 273   | 187 | BB  | Û    | 333   | 219 | DB  | û    | 373   | 251 | FB  |

| œ    | 234   | 156 | 9C  | ¼    | 274   | 188 | BC  | Ü    | 334   | 220 | DC  | ü    | 374   | 252 | FC  |

|      | 235   | 157 | 9D  | ½    | 275   | 189 | BD  | Ý    | 335   | 221 | DD  | ý    | 375   | 253 | FD  |

|      | 236   | 158 | 9E  | ¾    | 276   | 190 | BE  | Þ    | 336   | 222 | DE  | þ    | 376   | 254 | FE  |

| Ý    | 237   | 159 | 9F  | ¸    | 277   | 191 | BF  | Þ    | 337   | 223 | DF  | ÿ    | 377   | 255 | FF  |

## Aspects of Computer Architecture

### Character Codes

#### 3.4. Unicode Character Codes

In order to deal with the many character sets used in the written languages of the world, the Unicode Character Codes were developed over the last decade. The standard allows 8, 16, or 32 bit definitions of the characters. The following URL contains the details, and there are many, of the Unicode effort.

<http://www.unicode.org/>

The table below contains the lay out of the Unicode Character Sets.

<http://www.unicode.org/Public/UNIDATA/Blocks.txt>

```

# Unicode Character Database

# Copyright (c) 1991-2004 Unicode, Inc.

# For terms of use, see http://www.unicode.org/terms_of_use.html

# For documentation, see UCD.html

```

## Aspects of Computer Architecture

### Character Codes

Table 10 UNICODE Character Codes

|      |      |                                       |      |      |                                         |        |       |                                         |

|------|------|---------------------------------------|------|------|-----------------------------------------|--------|-------|-----------------------------------------|

| 0000 | 007F | Basic Latin                           | 2070 | 209F | Superscripts and Subscripts             | 4DC0   | 4DFF  | Yijing Hexagram Symbols                 |

| 0080 | 00FF | Latin-1 Supplement                    | 20A0 | 20CF | Currency Symbols                        | 4E00   | 9FFF  | CJK Unified Ideographs                  |

| 0100 | 017F | Latin Extended-A                      | 20D0 | 20FF | Combining Diacritical Marks for Symbols | A000   | A48F  | Yi Syllables                            |

| 0180 | 024F | Latin Extended-B                      | 2100 | 214F | Letterlike Symbols                      | A490   | A4CF  | Yi Radicals                             |

| 0250 | 02AF | IPA Extensions                        | 2150 | 218F | Number Forms                            | AC00   | D7AF  | Hangul Syllables                        |

| 02B0 | 02FF | Spacing Modifier Letters              | 2190 | 21FF | Arrows                                  | D800   | DB7F  | High Surrogates                         |

| 0300 | 036F | Combining Diacritical Marks           | 2200 | 22FF | Mathematical Operators                  | DB80   | DBFF  | High Private Use Surrogates             |

| 0370 | 03FF | Greek and Coptic                      | 2300 | 23FF | Miscellaneous Technical                 | DC00   | DFFF  | Low Surrogates                          |

| 0400 | 04FF | Cyrillic                              | 2400 | 243F | Control Pictures                        | E000   | F8FF  | Private Use Area                        |

| 0500 | 052F | Cyrillic Supplement                   | 2440 | 245F | Optical Character Recognition           | F900   | FAFF  | CJK Compatibility Ideographs            |

| 0530 | 058F | Armenian                              | 2460 | 24FF | Enclosed Alphanumerics                  | FB00   | FB4F  | Alphabetic Presentation Forms           |

| 0590 | 05FF | Hebrew                                | 2500 | 257F | Box Drawing                             | FB50   | FDFF  | Arabic Presentation Forms-A             |

| 0600 | 06FF | Arabic                                | 2580 | 259F | Block Elements                          | FE00   | FE0F  | Variation Selectors                     |

| 0700 | 074F | Syriac                                | 25A0 | 25FF | Geometric Shapes                        | FE20   | FE2F  | Combining Half Marks                    |

| 0780 | 07BF | Thaana                                | 2600 | 26FF | Miscellaneous Symbols                   | FE30   | FE4F  | CJK Compatibility Forms                 |

| 0900 | 097F | Devanagari                            | 2700 | 27BF | Dingbats                                | FE50   | FE6F  | Small Form Variants                     |

| 0980 | 09FF | Bengali                               | 27C0 | 27EF | Miscellaneous Mathematical Symbols-A    | FE70   | FEFF  | Arabic Presentation Forms-B             |

| 0A00 | 0A7F | Gurmukhi                              | 27F0 | 27FF | Supplemental Arrows-A                   | FF00   | FFEF  | Halfwidth and Fullwidth Forms           |

| 0A80 | 0AFF | Gujarati                              | 2800 | 28FF | Braille Patterns                        | FFF0   | FFFF  | Specials                                |

| 0B00 | 0B7F | Oriya                                 | 2900 | 297F | Supplemental Arrows-B                   | 10000  | 1007F | Linear B Syllabary                      |

| 0B80 | 0BFF | Tamil                                 | 2980 | 29FF | Miscellaneous Mathematical Symbols-B    | 10080  | 100FF | Linear B Ideograms                      |

| 0C00 | 0C7F | Telugu                                | 2A00 | 2AFF | Supplemental Mathematical Operators     | 10100  | 1013F | Aegean Numbers                          |

| 0C80 | 0CFF | Kannada                               | 2B00 | 2BFF | Miscellaneous Symbols and Arrows        | 10300  | 1032F | Old Italic                              |

| 0D00 | 0D7F | Malayalam                             | 2E80 | 2EFF | CJK Radicals Supplement                 | 10330  | 1034F | Gothic                                  |

| 0D80 | 0DFF | Sinhala                               | 2F00 | 2FDF | Kangxi Radicals                         | 10380  | 1039F | Ugaritic                                |

| 0E00 | 0E7F | Thai                                  | 2FF0 | 2FFF | Ideographic Description Characters      | 10400  | 1044F | Deseret                                 |

| 0E80 | 0EFF | Lao                                   | 3000 | 303F | CJK Symbols and Punctuation             | 10450  | 1047F | Shavian                                 |

| 0F00 | 0FFF | Tibetan                               | 3040 | 309F | Hiragana                                | 10480  | 104AF | Osmanya                                 |

| 1000 | 109F | Myanmar                               | 30A0 | 30FF | Katakana                                | 10800  | 1083F | Cypriot Syllabary                       |

| 10A0 | 10FF | Georgian                              | 3100 | 312F | Bopomofo                                | 1D000  | 1D0FF | Byzantine Musical Symbols               |

| 1100 | 11FF | Hangul Jamo                           | 3130 | 318F | Hangul Compatibility Jamo               | 1D100  | 1D1FF | Musical Symbols                         |

| 1200 | 137F | Ethiopic                              | 3190 | 319F | Kanbun                                  | 1D300  | 1D35F | Tai Xuan Jing Symbols                   |

| 13A0 | 13FF | Cherokee                              | 31A0 | 31BF | Bopomofo Extended                       | 1D400  | 1D7FF | Mathematical Alphanumeric Symbols       |

| 1400 | 167F | Unified Canadian Aboriginal Syllabics | 31F0 | 31FF | Katakana Phonetic Extensions            | 20000  | 2A6DF | CJK Unified Ideographs Extension B      |

| 1680 | 169F | Ogham                                 | 3200 | 32FF | Enclosed CJK Letters and Months         | 2F800  | 2FA1F | CJK Compatibility Ideographs Supplement |

| 16A0 | 16FF | Runic                                 | 3300 | 33FF | CJK Compatibility                       | E0000  | E007F | Tags                                    |

| 1700 | 171F | Tagalog                               | 3400 | 4DBF | CJK Unified Ideographs Extension A      | E0100  | E01EF | Variation Selectors Supplement          |

| 1720 | 173F | Hanunoo                               |      |      |                                         | F0000  | FFFFF | Supplementary Private Use Area-A        |

| 1740 | 175F | Buhid                                 |      |      |                                         | 100000 | 10FFF | Supplementary Private Use Area-B        |

| 1760 | 177F | Tagbanwa                              |      |      |                                         |        |       |                                         |

| 1780 | 17FF | Khmer                                 |      |      |                                         |        |       |                                         |

| 1800 | 18AF | Mongolian                             |      |      |                                         |        |       |                                         |

| 1900 | 194F | Limbu                                 |      |      |                                         |        |       |                                         |

| 1950 | 197F | Tai Le                                |      |      |                                         |        |       |                                         |

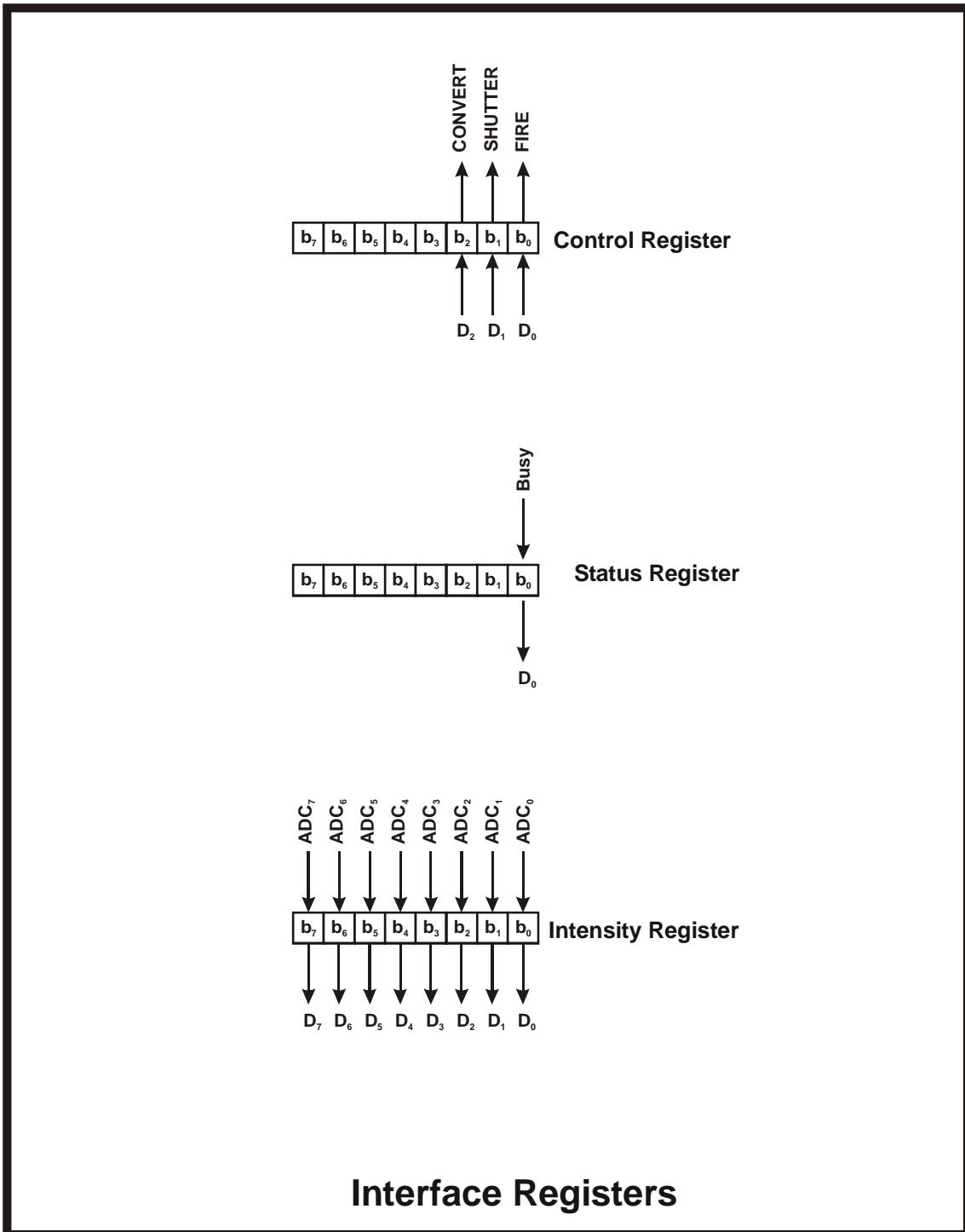

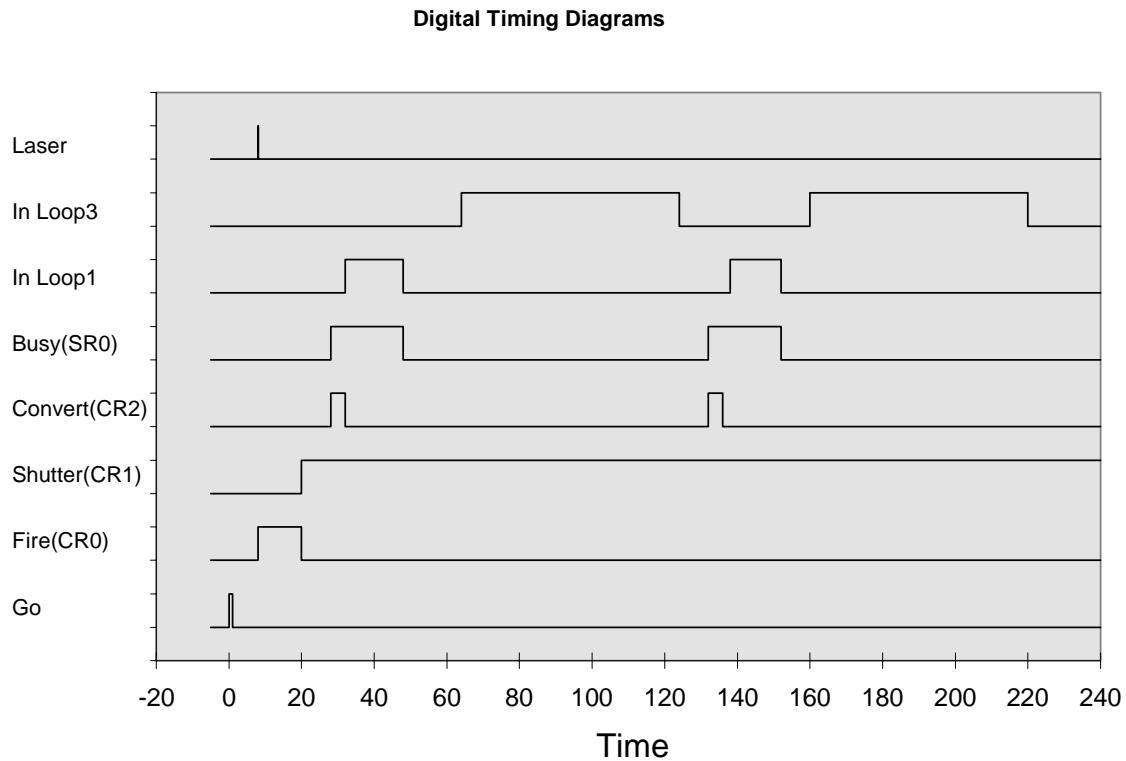

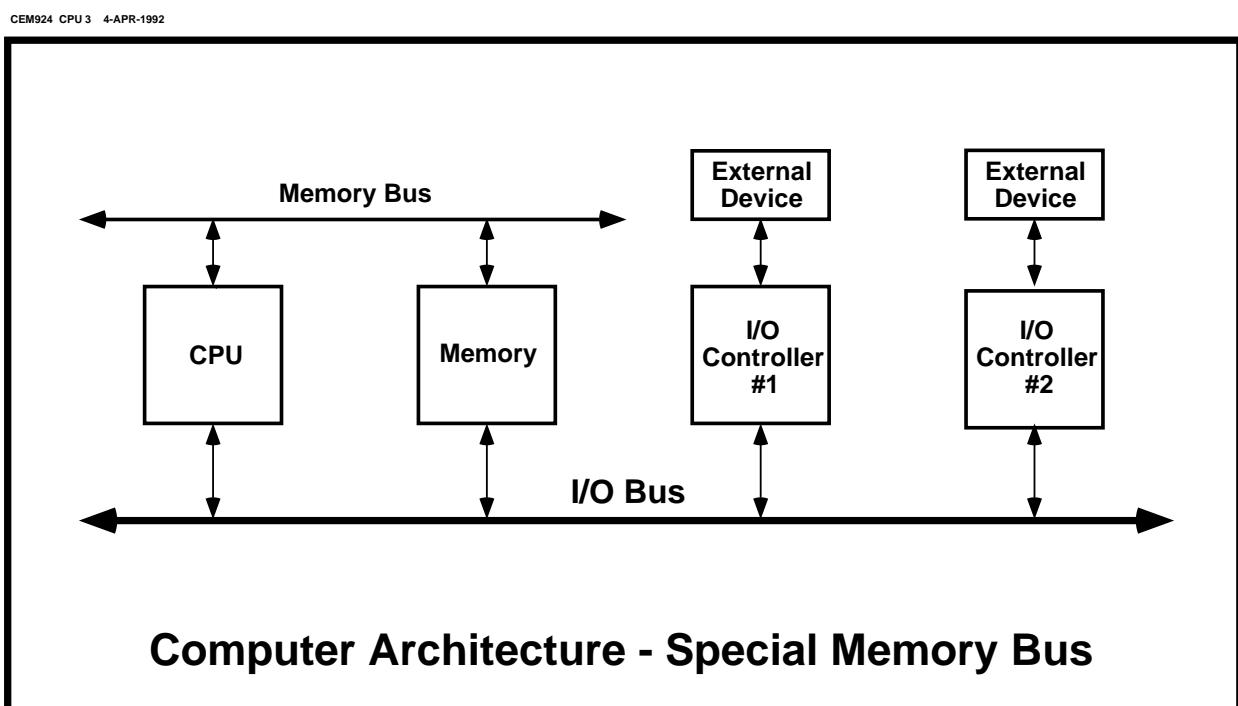

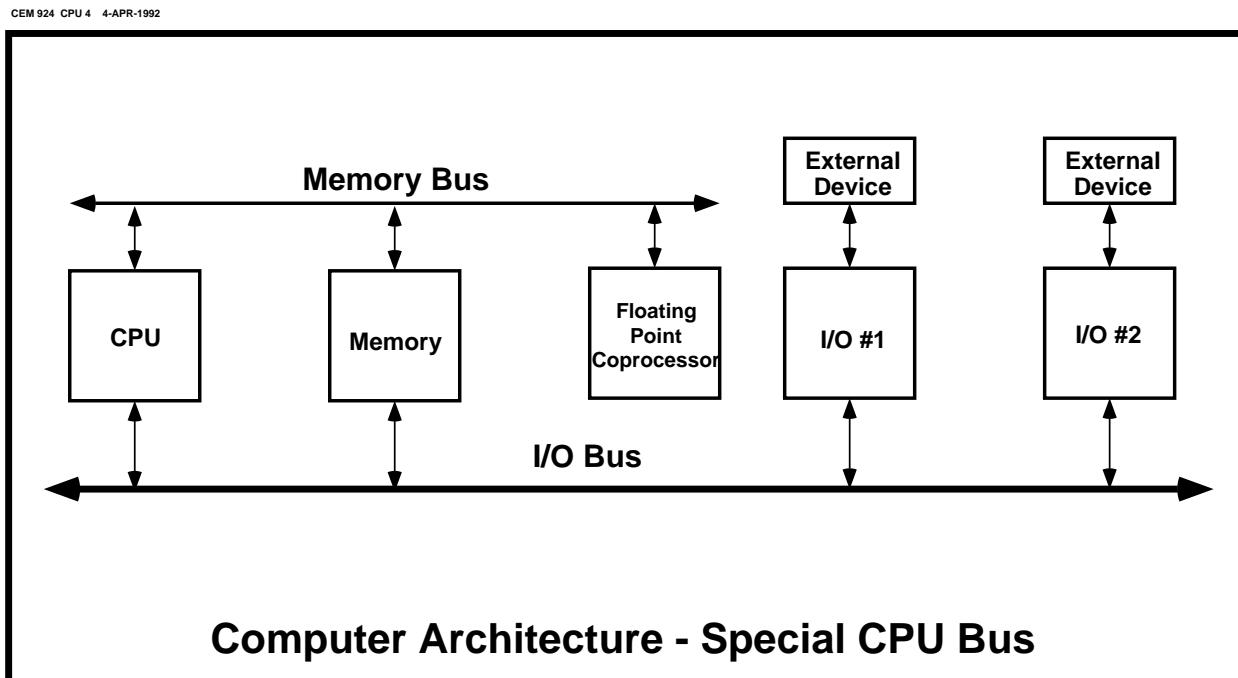

| 19E0 | 19FF | Khmer Symbols                         |      |      |                                         |        |       |                                         |